## Digital RF transmitter with single-bit $\Delta\Sigma$ M-driven switched-capacitor RF DAC and embedded band filter in 28-nm FD-SOI

Razvan-Cristian Marin, Antoine Frappé, Bruno Stefanelli, Philippe Cathelin, Andreia Cathelin, Andreas Kaiser

#### ▶ To cite this version:

Razvan-Cristian Marin, Antoine Frappé, Bruno Stefanelli, Philippe Cathelin, Andreia Cathelin, et al.. Digital RF transmitter with single-bit  $\Delta\Sigma$  M-driven switched-capacitor RF DAC and embedded band filter in 28-nm FD-SOI. IEEE Transactions on Microwave Theory and Techniques, 2019, 67 (7), pp.3200-3209. 10.1109/TMTT.2019.2897929 . hal-02314498

### HAL Id: hal-02314498 https://hal.univ-lille.fr/hal-02314498v1

Submitted on 20 Oct 2019

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Digital RF Transmitter With Single-Bit ΔΣM-Driven Switched-Capacitor RF DAC and Embedded Band Filter in 28nm FD-SOI

Răzvan-Cristian Marin, *Member, IEEE*, Antoine Frappé, *Senior Member, IEEE*, Bruno Stefanelli, *Member, IEEE*, Philippe Cathelin, Andreia Cathelin, *Senior Member, IEEE*, and Andreas Kaiser, *Senior Member, IEEE*

Abstract—This paper presents a single-bit RF transmitter based on single-bit switched-capacitor RF digital-to-analog converters (DAC) embedded in an FIR filter (FIR-DAC). The transmitter system comprises a single-bit quadrature Delta-Sigma Modulator (ΔΣΜ), a digital mixer, and a 109-tap RF FIR-DAC stage with a single external inductor, combining D-A conversion with discrete and continuous time filtering. The onchip part of the FIR-DAC is built exclusively with CMOS inverters and Metal-Oxide-Metal (MOM) capacitors, which are implemented in the interconnect layers to propose a compact fully-digital solution, suitable for advanced CMOS nodes. A method for canceling redundant switching in the FIR-DAC is proposed to reduce its complexity and power consumption. Combining discrete and continuous-time filtering, the out-ofband quantization noise of the 1-bit RF signal is strongly attenuated below the level required by emission masks. The RF FIR-DAC prototype is implemented in 28nm FD-SOI CMOS technology with 10 metal layers and occupies a total active area of only 0.047 mm<sup>2</sup>. The overall power consumption is 38 mW at 4.6 dBm peak output power, 900 MHz carrier frequency and 1 V supply. FD-SOI body-bias Vt tuning is used to effectively correct mixing clock duty-cycle errors in order to perform precise highfrequency I/O interleaving, which enables high image and local oscillator (LO) rejections. The resulting power consumption, surface and performance of the measured prototype make the proposed circuits and concepts particularly appropriate for use in emerging Internet of Things (IoT) applications.

Index Terms—All-digital transmitter, body-bias, Delta-Sigma modulation ( $\Delta\Sigma$ M), finite impulse response filter (FIR), FIR-DAC, switched-capacitor (SC) DAC, 28nm FD-SOI.

#### I. INTRODUCTION

CONSTANT technology downscaling drives the transition from analog to digital-intensive transmitters for integrated

Manuscript received October 13, 2018; revised January 7, 2019; This work was supported in part by the Nano 2017 program in the frame of the ST-IEMN common lab, in part by STMicroelectronics, in part by the Hauts-de-France Region and in part by the Research Council of the Catholic University of Lille.

R.-C. Marin, A. Frappé, B. Stefanelli, and A. Kaiser are with the University of Lille, also with CNRS, also with Centrale Lille, also with ISEN, also with University of Valenciennes, and also with UMR 8520 - IEMN, F-59000 Lille, France (e-mail: cristian.marin@yncrea.fr).

P. Cathelin and A. Cathelin are with STMicroelectronics, 38926 Crolles Cedex, France.

mobile devices developed to support emerging Internet of

Things (IoT) applications [1]. Recent research concentrates on the complete System-on-Chip (SoC) implementation of the transmit chain, as well as pushing the digital signal processing domain boundary closer to the antenna.

The main challenges specific to digital transmitter design are to reduce quantization noise below spectrum mask requirements, to achieve power consumption levels similar or below analog/RF transmitters and to reach carrier frequencies in the GHz range. Proposed approaches in literature range from high-resolution high-speed digital-to-analog converters (DAC) to single-bit Delta-Sigma modulated digital RF signals at multi-GHz clock rates.

#### A. Speed vs. resolution trade-off in digital transmitters

Various trade-offs between resolution and clock rates have been used in digital to RF conversion (DRFC) approaches, embedding the DAC into the baseband to RF mixer. Examples are the 6-bit switched-capacitor (SC) I/Q sharing DRFC structure in [2] or the 13-bit RF power DAC in [3], which present significant conceptual differences, since [2] optimizes power efficiency using a low-resolution scheme, and [3] targets improved noise performance thanks to additional resolution and digital pre-distortion. In [4], a 10-bit current-steering DAC is demonstrated and digital Delta-Sigma Modulators ( $\Delta\Sigma$ M) with mismatch shaping (MS) are used to reduce OOB emissions at a programmable duplex distance. Similarly, a 12-bit resistive quadrature DAC (RQDAC) is presented in [5] with incremental-charge based operation to reduce the power consumption required to drive the RF load.

Low-resolution  $\Delta\Sigma$ M-based architectures [6], [7] have the potential to achieve excellent in-band performance and be efficiently integrated in CMOS technologies. On the one hand, the architecture in [6] introduces a 4-bit  $\Delta\Sigma$ M driving a 1-bit pulse width modulator (PWM), which enables the use of an efficient class-G switched-capacitor PA, similar to [8]. On the other hand, in [7] an all-digital RF signal generator is designed based on single-bit low-pass  $\Delta\Sigma$ Ms and a simplified digital mixer, thus opening the way towards the implementation of an all-digital transmitter scheme based on switching-mode (SM) power amplifier (PA).

©IEEE Version submitted for final publication in

#### B. Known filtering techniques

One solution to reduce out-of-band quantization noise is to introduce highly selective analog filtering. Bulk acoustic wave (BAW) filters have been developed for mobile RF-front-ends with significantly higher quality factors (Q up to 1000) than on-chip *LC* tanks, better temperature stability and power handling capability compared to surface acoustic wave (SAW) devices, and the potential to be fabricated in above-IC approach [9]. However, manufacturing cost and yield issues have so far limited above-IC integration at an industrial scale.

Semi-digital solutions based on finite impulse response (FIR) filters represent another attractive approach, thanks to the possibility of digitally adjusting the transfer function. In [10], a parallel DRFC structure is introduced to create a 2-tap FIR filter with two notches at  $\pm 500$  MHz from the 2.45 GHz center frequency. A 5-channel power combiner based on transmission lines was proposed in [11], allowing a digitally reconfigurable RF FIR filter with binary coefficients. A similar approach was used in [12], integrating a power combiner using on-chip transformers in a 3-tap FIR configuration. The measured noise floor is -149 dBc/Hz in a selected 20 MHz band, whereas the  $3.4 \Omega$  output resistance enables 30 dBm peak output power. In addition, a 6-tap FIR-DAC is introduced in [13] based on 1-bit band-pass (BPF)  $\Delta\Sigma$ -DAC and a current-steering FIR reconstruction filter with programmable zero location based on 6-tap digital delay line. These FIR-based quantization noise filtering techniques propose to create notches in the OOB noise spectrum using few taps for the filtering function. To provide a global out-ofband attenuation over the complete spectrum, [14] suggested a 63-tap semi-digital FIR-DAC in a differential current-steering architecture targeting 60 dB stopband attenuation for 802.11 ac/ad signals.

In this paper, a low-power 109-tap RF FIR-DAC taking advantage of a switched-capacitor structure designed for single-bit  $\Delta\Sigma$  RF signals is presented. Section II describes the theory of the digital transmit chain and the study of the FIR-DAC non-idealities model. Next, Section III details the 28nm FD-SOI CMOS circuit implementation, emphasizing the integration of the FIR-DAC under a signal pad. The proposed concept is validated with measurement results in Section IV, and Section V concludes this paper.

#### II. THEORY OF OPERATION

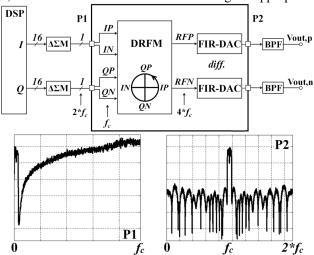

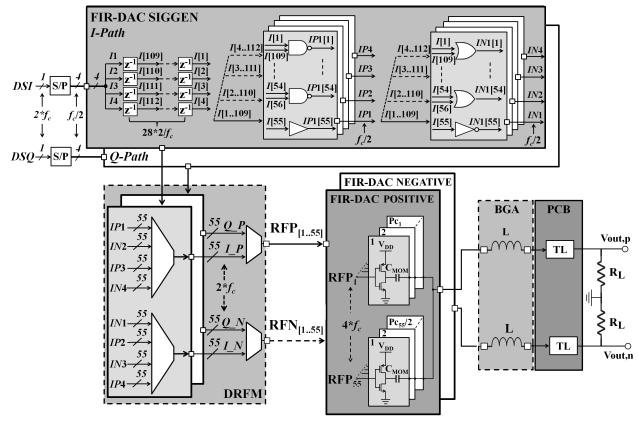

The proposed all-digital RF transmitter architecture is shown in Fig. 1. It comprises two quadrature 1-bit  $3^{\rm rd}$  order  $\Delta\Sigma$ Ms, working synchronously at twice the carrier frequency  $(f_c)$ , a digital mixer (DRFM) producing a digital RF signal at the final sample rate of  $4*f_c$ , a pseudo-differential RF DAC with embedded FIR filtering, and an *RLC* band-pass filter.

The digital mixing process is simplified by setting the sampling frequency to  $f_s = 4*f_c$  [7], allowing the cosine and sine versions of the LO signal period to be expressed as simple sequences, namely {1; 0; -1; 0} and {0; 1; 0; -1}. In this case,

one out of two values in the I and Q paths can be dropped. Thus, the mixer is reduced to time-interleaving the appropriate

Fig. 1. Proposed all-digital RF transmitter architecture and conceptual representation of the 1-bit digital input signal spectrum and the analog output signal spectrum of the transmitter.

Fig. 2. Conceptual view of the proposed N-length FIR-DAC.

I and Q path samples with positive (IP/QP) or negative (IN/QN) polarity. The resulting mixer output over one LO period can be represented by the sequence  $\{IP; QP; IN; QN\}$  at the sampling frequency  $4*f_c$ . Hence, by generating only the useful I and Q samples, the effective sampling rate of the  $\Delta\Sigma$ M stage can be reduced to  $2*f_c$ . Additionally, time interleaving of the  $\Delta\Sigma$ Ms enables multi-GHz carrier frequency operation, as shown in [15].

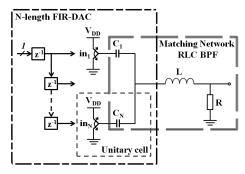

Furthermore, the constant-level switching at the output of the  $\Delta\Sigma M$  allows the implementation of N 1-bit switched-capacitor DACs, which are recombined to form an FIR filter. The FIR filter function is embedded into the DAC by introducing delays between N successive driver/capacitor sections, which correspond to N delayed versions of the single-bit  $\Delta\Sigma M$  output (Fig. 2). Relative sizes of capacitors are used to implement arbitrary coefficients in the FIR filter, which has linear phase, thanks to the symmetrical capacitor ratios, i.e.  $C_i = C_{N-i+1}$ , where i = 1...N/2.

Combinations of elementary DAC cells can be used to create programmable coefficients of an N-tap digital FIR filter, embedded in the DAC stage. With respect to its current-source counterpart, the SC scheme has the advantages that it does not require stringent transistor matching and has constant

impedance seen from the output. Furthermore, in a switched-capacitor DAC, signals can be combined on an inductor in series with the load [16]. The total DAC capacitance and the inductor form the LC matching network to the load resistance, where L and C are tuned to resonate at the carrier frequency. The band-pass filter created around  $f_c$  contributes to quantization noise filtering, thus being highly useful in relaxing the design constraints of the FIR filter.

#### A. FIR filter design optimization

In a conventional DAC, the number of bits is set according to the target minimum noise floor, even though the OOB noise requirements are not uniform over the entire spectrum. To avoid overdesign, a configurable FIR filter is used to i) set a lower overall target noise rejection of 70 dBc, and ii) adjust the zeros placement to target 80 dBc noise rejection only at specific frequency bands for multi-standard coexistence. We note that 80 dBc corresponds approximately to the thermal noise floor, when considering a 20 MHz channel bandwidth, a succeeding power amplifier with an average output power of 20 dBm, and 40 dB isolation from antenna to antenna [17].

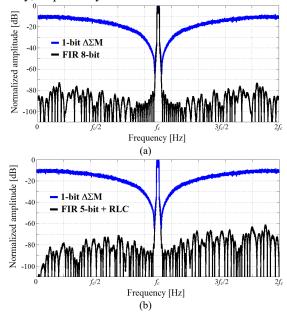

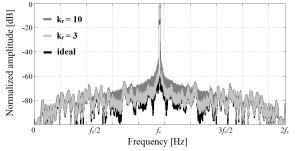

The FIR filter was designed in MATLAB using a window method, i.e. convolution in frequency domain between the ideal impulse response filter and a window function to derive a finite impulse response filter. Different types of integration windows (same conditions on filter length and coefficient quantization) were evaluated, in order to obtain a trade-off between near-band and far-out-of-band noise attenuation. The  $\Delta\Sigma$ M is designed according to [15] as a single-bit 3<sup>rd</sup> order CIFB (Cascade-of-integrators feedback form) with quantized coefficients and OSR (oversampling ratio) of 100, resulting in a peak SNR (signal to noise ratio) of ~90 dB, and requires extensive filtering of the quantization noise, as shown in Fig. 3(a). The required performance can be achieved by an FIR filter using a Hann window [18] with 109 symmetric coefficients quantized to 8 bits. The total number of unitary filter taps, i.e. DAC cells, is estimated by summing the 109 quantized coefficients (lowest is 1, largest is 256), which adds up to ~14500. Hence, building such a filter is not physically feasible, as it would produce a tremendous overhead in wiring, which will negatively impact electrical performance.

The first optimization step is to co-design the FIR filter together with the output *RLC* band-pass filter (Fig. 3(b)). By relaxing the filtering constraints, the resolution of the FIR coefficients can be reduced to 5 bits (largest is 32), which lowers complexity by 8 times (1800 total unitary cells), and facilitates integration in advanced CMOS technology nodes.

#### B. FIR-DAC architecture optimization

The second optimization step addresses the optimization of the switched-capacitor scheme, by reducing switching redundancy and power consumption

$$P_{SC} = \alpha_{SC} \cdot C_T \cdot V_{DD}^2 \cdot f_s \tag{1}$$

where the factor  $\alpha_{SC}$  represents the contribution of the singlebit  $\Delta\Sigma M$  (driving N delayed paths of the FIR-DAC) switching activity to the average dissipated energy,  $C_T$  is the total output node capacitance,  $V_{DD}$  the supply voltage, and  $f_s$  the sampling frequency, respectively.

Fig. 3. Output spectrum: (a), (b) 1-bit  $\Delta\Sigma$ M; (a) FIR with 8-bit coefficient quantization; (b) FIR with 5-bit coefficient quantization and *RLC* filter.

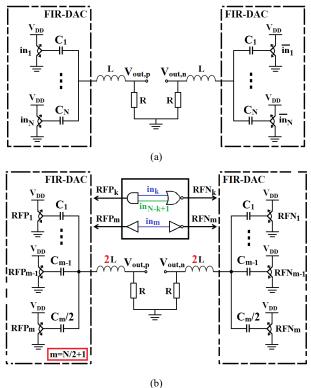

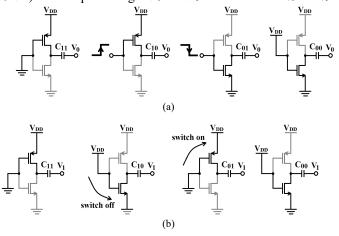

Let us consider the differential FIR-DAC structure in Fig. 4(a). Taking into account that during fast transitions the inductor can be seen as an open circuit, we identify that when the digital inputs  $in_k$  and  $in_{N-k+1}$  to symmetric FIR coefficients  $(C_k = C_{N-k+1})$  have opposite values, the resulting contribution on the differential output is zero. Switching redundancy is cancelled by introducing AND/NOR gates on the positive/negative sides of the FIR-DAC, which allows an estimated switching activity reduction of ~20%.

Therefore, the FIR-DAC driving signals for k = 1..54 and m = N/2 + 1 = 55 are:

$$\begin{cases} RFP_k = RFP_{N-k+1} = in_k \ AND \ in_{N-k+1} & RFP_m = in_m \\ RFN_k = RFN_{N-k+1} = in_k \ NOR \ in_{N-k+1} & RFN_m = in_m \end{cases}$$

(2)

Now, both symmetric coefficients and corresponding driving signals are equivalent. As a result, the symmetric sides become redundant and one side of the filter is simply removed (Fig. 4(b)). Though it is a classic technique in digital FIR filter design, it is the first time it has been applied to FIR-DAC design, being driven by the need to implement a very large number of FIR coefficients.

Hence, 109-tap FIR filter performance can be achieved using only half the filter coefficients, namely 55 out of 109, whereas the coefficients  $C_{1...54}$  keep their initial value and the middle non-symmetric coefficient  $C_{55}$  is halved. In practice, this translates to the digital signal processing of 109 consecutive samples, to obtain 55 signal streams  $RF_{1...55}$  which drive 55 DAC cell groups. With respect to the straight-forward approach, the FIR complexity is reduced by 16 times in terms of total number of cells, and 2 times in terms of number of signal streams for similar OOB noise performance. Thus, for a

constant unitary capacitance, the inductance value is doubled to maintain the same resonance frequency of the LC network

Fig. 4. Differential FIR-DAC: (a) conventional; (b) optimized with reduced switching activity and number of unitary cells.

(the total output node capacitance is halved), which also changes the RLC quality factor. Moreover, the three remaining possible combinations of positive and negative driving signals,  $RFP/RFN = \{1/0; 0/0; 0/1\}$ , result in a pseudo-differential configuration, which might cause increased even-order harmonics due to non-ideal differential to single-ended conversion. Finally, the key advantage of the proposed architecture is that it combines the increased output power of the differential architecture with the performance of the single-ended architecture in terms of switching power, area, number of unitary cells and input signal drivers.

#### C. FIR-DAC switching model

A comprehensive study of the switching model for switched-capacitor PA schemes is shown in [16], where the unitary PA cells are activated based on the input signal amplitude during the first half-period, whereas in the second half, all the cells are switched-off, so that the switching power does not depend on the cell switching transitions. However, in the proposed architecture (Fig. 4), the unitary cells are de-/activated during a complete time period, based on the control signals derived in the FIR filter, meaning that the switching scheme model has to take into consideration also the previous state (on/off) of the cells (transitions). To evaluate the average switching power, the simplified switching model in Fig. 5 is considered at the switching instants  $t_0$  and  $t_1$ . The capacitances are denoted  $C_{ij}$ , where the first index i corresponds to the

connection of the bottom plate at time  $t_0$ , and the second index j corresponds to time  $t_1$  ("1" denotes  $V_{DD}$  and "0" denotes GND). The output voltages  $V_0$  and  $V_1$  at time instants  $t_0$  and  $t_1$

Fig. 5. 2-bit SC scheme: switching activity from time instant  $t_0$  (a) to  $t_1$  (b); On-transistors are depicted in black and off-transistors in grey.

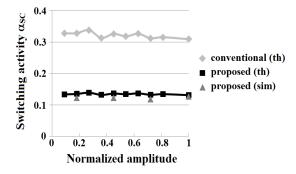

Fig. 6. Switching activity  $\alpha_{SC}$  as function of the input signal amplitude; validation of the theoretical switching model by Spectre simulations.

are obtained from the ratio between switched-on capacitances and the total capacitance  $C_T$  times the supply voltage  $V_{DD}$

$$\begin{cases} V_0 = \frac{C_{11} + C_{10}}{C_T} \cdot V_{DD} \\ V_1 = \frac{C_{11} + C_{01}}{C_T} \cdot V_{DD} \end{cases}$$

(3)

The average switching power  $P_{SC}$  can be expressed as the total energy  $E_x$  spent during  $N_P$  periods divided by the number of periods  $N_P$  and the sampling period  $T_S = 1/(4*f_c)$

$$P_{SC} = \frac{1}{N_P \cdot T_s} \cdot \sum_{i=1}^{N_P} E_{x,i} \tag{4}$$

Combining (1) and (4), the average switching activity  $\alpha_{SC}$  is computed with the voltage drop difference on  $C_{ij}$

$$\alpha_{SC} = \frac{\sum_{i=1}^{N_P} \alpha_{10,i} \cdot (\alpha_{01,i} + \alpha_{11,i}) + \alpha_{01,i} \cdot (\alpha_{10,i} + \alpha_{00,i})}{N_P}$$

(5)

where all the capacitances  $C_{ij}$  are normalized to the total capacitance  $C_T$ , namely  $\alpha_{ij} = C_{ij} / C_T$ .

Hence, considering (5), the power consumption is reduced

by  $\sim$ 60% in the case of the proposed FIR-DAC (Fig. 4(b)), with respect to the conventional scheme (Fig. 4(a)) for the same OOB noise performance, thanks to optimized switching (20%), and architecture simplification (50%).

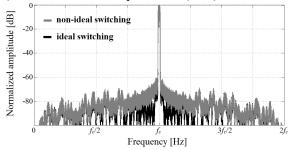

Fig. 7. Output spectrum: ideal and non-ideal switching  $-\sigma_{tr/tf} = 0.5\% \cdot T_s$ ,  $\sigma_{PLH/PHL} = 0.5\% \cdot T_s$ ,  $\sigma_{f,var} = 1\% \cdot T_s$ .  $\sigma_{f,var} \approx 2.8$  ps when  $f_c = 900$  MHz.

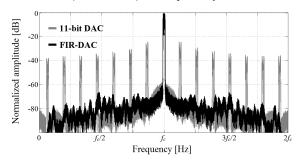

Fig. 8. Output spectrum: coefficient mismatch - standard deviation 10%; Comparison with 11-bit RF DAC with ideal upconversion.

This is highlighted in Fig. 6, in addition to the validation of the switching model combining (1) and (5) using behavioral Spectre RF simulations. We may remark that the switching activity is almost independent of the input signal amplitude (before DSM). Furthermore, generating only 55 out of 109 signal streams leads to a significant reduction of complexity and power consumption of the FIR-DAC driving circuit.

#### D. FIR-DAC non-idealities model

In this section, a model for the unitary DAC cell nonidealities is proposed and the impact of circuit integration on the FIR filter function is evaluated. First, the switch driving signals RFP/RFN are subject to non-idealities due to rise/fall time  $(t_r/t_f)$ , propagation delays  $(t_{PLH}/t_{PHL})$  and jitter  $(t_{j,var})$ . We assume that all parameters are specific to each path and normally distributed, with  $\Delta t_r$ ,  $\Delta t_f$ ,  $\Delta t_{PLH}$ , and  $\Delta t_{PHL}$  constant throughout simulation, and variable cycle-to-cycle  $t_{j,var}$ . System-level simulations reveal that jitter causes the main noise performance degradation, rendering part of the FIR filter zeros indistinct compared to the ideal case. Still, when considering the combined switching non-idealities (Fig. 7), we remark that the noise level near the signal-band is lower than in the case of jitter only, which may be accounted for by a slight cancellation effect between the variable propagation delay and jitter which lowers overall deviation.

A different source of non-ideality arises from the matching errors of the unitary capacitances, which directly impacts the FIR filter coefficients and transfer function (Fig. 8). It is seen that for large deviations, the proposed FIR-DAC can achieve a noise attenuation performance similar to a conventional 11-bit RF DAC at specific critical bands. Also, the proposed scheme does not create additional signal images, like in an RF DAC [19], where a trade-off is made to reduce baseband sampling

Fig. 9. Output spectrum: effect of voltage supply variation with respect to the tolerated supply resistance  $k_r$ .

frequency and power consumption. The 11-bit RF DAC is modelled as in [19], with 1/3 of the total number of bits binary and 2/3 thermometer coded, respectively.

Moreover, the variation of the voltage supply has a significant impact on both switching and coefficient non-idealities (Fig. 9), because it is mainly dependent on the cycle-to-cycle switching current  $I_{SC}$  and it may become critical in high-frequency switching schemes. The supply variation is defined here as  $\Delta V_{DD} = k_r \cdot I_{SC}$ , where  $k_r$  is used to derive the tolerated supply resistance for the filter transfer function. We note that an increase of  $k_r$  determines a gradual degradation of the near-band noise performance.

Finally, the signal-band performance of the proposed FIR-DAC is evaluated in the presence of non-idealities, showing very good EVM (error vector magnitude) performance, when applying static correction of the I/Q constellation similar to [20]. In the case of an orthogonal frequency-division multiplexing (OFDM) 20 MHz 16QAM (quadrature amplitude modulation) signal, the resulting rms EVM of the transmit chain is close to 1.5%.

#### III. CIRCUIT DESCRIPTION

A top-level schematic of the proposed digital RF transmit chain is presented in Fig. 10. The digital inputs DSI and DSQ are single-bit  $\Delta\Sigma$  modulated signals generated externally, and a serial-to-parallel (S/P) converter was inserted to reduce digital core operating frequency, leading to a 4-phase system configuration on both I and Q paths at a sample rate  $f_c/2$ . The FIR-DAC SIGGEN blocks generate the baseband level delayed control signal groups, in the I and Q paths, for the 55 switching blocks of the FIR-DAC. Finally, the groups are processed by digital RF mixers (DRFM), which work as interconnection matrixes to derive the digital streams at  $4*f_c$ , namely  $RFP = \{IP1, QP1, IP2, QP2, IP3, QP3, IP4, QP4\}$ , and  $RFN = \{IN1, QN1, IN2, QN2, IN3, QN3, IN4, QN4\}$ , which drive the switching blocks of the positive and negative sides of the pseudo-differential FIR-DAC.

#### A. Digital RF signal generation

The FIR-DAC SIGGEN block uses the output of a single-bit quadrature  $\Delta\Sigma M$  to provide the necessary signals that

implement (2) to perform the FIR filter simplification. At the input, a shift register holds 112 consecutive samples I/O[1,...,112] at each time period  $(2/f_c)$ .

Fig. 10. All-digital RF transmit chain block diagram.

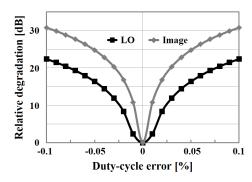

Fig. 11. Relative LO and image rejection degradation vs duty-cycle error

Furthermore, 4 groups of 55 signal streams per path (I/Q) and per side (positive/negative) are derived to drive the FIR-DAC. The DRFM block is implemented as a multiplexer (MUX) which reconstructs the RF signal streams  $RFP/N_{I....55}$  at  $4*f_c$ . Signal multiplexing is performed in two steps: 1) a 4:1 MUX driven by two clocks of frequency  $f_c/2$  and  $f_c$ , which creates the signals for the I and Q paths on the positive and negative sides at  $2*f_c$ , followed by 2) a 2:1 MUX driven by the main clock of frequency  $2*f_c$ , which interleaves the I and Q paths. Normally, the mixing process would require high frequency signal sampling at  $2*f_c$  (first step) and  $4*f_c$  (second step) for

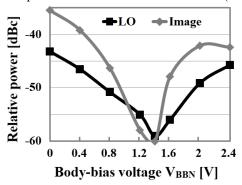

precise I/Q interleaving. Instead, we propose to use the FD-SOI body-bias  $V_t$  tuning feature [21] in the DRFM to adjust digital clock tree switching (equalize rise/fall times and propagation delays), and thus correct the clock duty-cycle

Fig. 12. Unitary cell 3D layout (3D GDSII Viewer).

errors (DCE) causing I/Q mismatch.

System-level simulations showed that clock DCE determine an overall degradation of the noise performance (including image, LO, noise floor) in the first multiplexing

step (separate I and Q paths) and introduce I/Q mismatch in the second multiplexing step (I/Q path interleaving), which mainly impacts the image rejection, as shown in Fig. 11 (for  $\Delta_{DCE} = \pm 0.1\%$ , where the duty cycle is  $DC = 50\% + \Delta_{DCE}$ ). In addition, an interface buffer is included between the digital RF signal generator and the FIR-DAC, according to a theoretical estimation of the line load in each path and an RC extraction of the output stage.

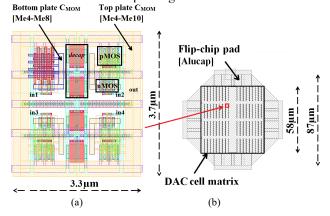

Fig. 13. (a) Group of 4 power cells; (b) DAC under FC pad.

Fig. 14. Die micrograph and IC mounted flip-chip BGA package cavity. The cavity includes also SMD inductors and decoupling capacitors.

The complete design of the digital blocks was done based on VHDL/Verilog descriptions with digital synthesis tools, although some custom design was needed at the interface with the FIR-DAC. The simulated power consumption of the digital core is estimated at ~16 mW, when operating at a center frequency  $f_c = 0.9$  GHz. Moreover, integrating the two  $\Delta\Sigma$ M would add ~6 mW power consumption, as described in [15].

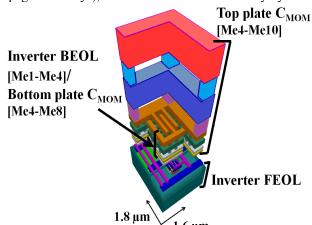

#### B. FIR-DAC circuit design

The unitary cell of the FIR-DAC comprises a CMOS inverter and a metal-oxide-metal (MOM) capacitor, which were co-designed to enable a performance optimization in terms of power consumption and area, achieving  $\sim 1.4 \,\mu\text{W}$  per GHz switching frequency for an area of  $1.6 \times 1.8 \,\mu\text{m}^2$ . The integration of the complete FIR-DAC under flip-chip (FC) RF pads is achieved through a specific multi-layer structure in a 10 metal (Me) process (3D view in Fig. 12).

The CMOS inverter is built up to Me1, inter-/intra-cell connections on Me2 to Me4, and the MOM capacitor on Me4 up to Me8 ( $C_{MOM} \approx 1.7$  fF), whereas the top-plates of

the capacitors are connected together directly to the pad on Me10 and Alucap. Furthermore, in order to reduce layout-induced parasitic elements on the output, unit cells are grouped by 4, which presents the following advantages:

- 1) The ring provides isolation between the cell groups;

- 2) There is no inner-group ring, thus reducing the parasitic capacitance seen at the output terminal;

- 3) The free space can be used for supply decoupling.

Fig. 15. Measured spectrum: 3 MHz single-tone at 6dB back-off.

The FIR-DAC has a total of 1152 unitary cells, divided into a 32 by 36 matrix to fit under the  $58x58 \mu m^2$  flip-chip pad (Fig. 13). Post-layout simulations of the FIR-DAC and the switching cells indicate a power consumption of 4 mW for the inverters and 2.5 mW for the capacitor banks, when operating in the 900 MHz band.

#### IV. EXPERIMENTAL RESULTS

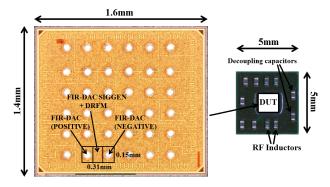

The circuit is fabricated in 28nm FD-SOI CMOS from STMicroelectronics and integrates the FIR-DAC SIGGEN, the DRFM and the FIR-DAC, with a total active area of 0.047 mm², including RF output pads. The IC is mounted on a 5x5 mm² dedicated flip-chip ball grid array (BGA), which embeds RF inductors to create the *LC* matching network, as well as additional decoupling capacitors. The device is connected to a dedicated printed circuit board (PCB), with RF differential output traces designed as adapted transmission lines at the targeted center frequency to complete the *RLC* filter. The chip micrograph and dedicated flip-chip BGA package are shown in Fig. 14.

The digital data inputs are generated externally in MATLAB, including the S/P conversion process, and streamed in using synchronized Tektronix AWG7000A arbitrary waveform generators at a clock rate  $f_{data} = f_c/2$ , whereas the main clock frequency is  $2*f_c$ . At the output, the differential to single-ended conversion is provided by an

Agilent E2695A RF probe, and the RF output is measured on  $50\Omega$  using a Keysight N9030A PXA signal analyzer.

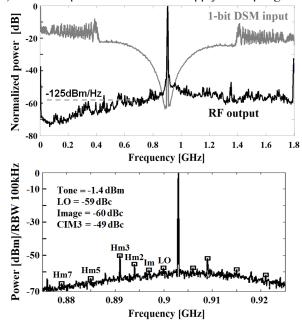

In Fig. 15, the measured output spectrum of a 3 MHz baseband (BB) single-tone at 6 dB back-off from the peak output power of 4.6 dBm emphasizes the out-of-band attenuation provided by the combined 109-tap FIR and *RLC* filtering. The in-band (100 MHz band) SNR is ~61 dB, which corresponds to 10 effective number of bits (ENOB).

Fig. 16. Measured duty-cycle error correction using wide range FD-SOI body-bias tuning

The carrier frequency is 900 MHz and the voltage supply is set to 1 V for an overall power consumption of 34.5 mW, out of which the RF output stage, differential RF FIR-DAC, consumes 8.3 mW and the digital blocks, FIR-DAC SIGGEN and DRFM, consume 26.2 mW. Measurements also confirm the results in Fig. 6 regarding the relatively constant switching power consumption in the FIR-DAC, regardless of the signal amplitude.

It was previously described that the 2-step MUX-based digital mixer is highly sensitive to clock duty-cycle errors (~30dB image rejection degradation at  $\Delta_{DCE} = \pm 0.1\%$ ). Duty-cycle errors can be corrected by tuning the body-bias voltage, which enables a balanced pMOS-nMOS switching operation. Fig. 16 highlights the efficiency of this mechanism in correcting DCE, thus finding an optimal operating point, where image and LO rejections are improved up to ~60 dBc at 6 dB back-off (~52 dBc at peak output power). With respect to Fig. 11, we remark similar LO and image rejection characteristics, from which we could estimate the body-bias compensation range, corresponding to a clock duty-cycle error  $|\Delta_{DCE}|$  < 0.05%.

Furthermore, it is seen that increased even-order harmonics are present in the output spectrum, due to the three-state output of the FIR-DAC, which is less effective for common mode rejection. Moreover, third order counter inter-modulation (CIM3) products at -49 dBc are present in the adjacent channel (Fig. 15), which is subject to stringent constraints in terms of spurious emissions. In [22] and [23], it is shown that CIM3 can be improved by canceling the signal third harmonic at  $3*f_c-f_{BB}$ , which intermodulates with the desired signal at  $f_c+f_{BB}$ , resulting in spurious emissions at  $f_c-3*f_{BB}$ , due to non-linearity.

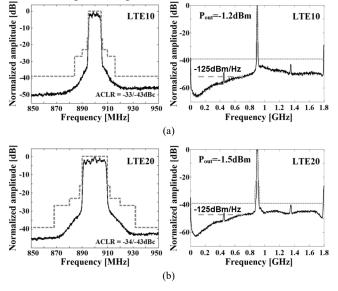

The measured spectrum for LTE 10 MHz (LTE10) and 20 MHz (LTE20) transmitted signals with 6 dB peak-to-

average power ratio (PAPR) is shown in Fig. 17. The average output power and ACLR for LTE10 are -1.2 dBm and -33/-43 dBc, whereas for LTE20 we obtained -1.5 dBm and -34/-43 dBc, respectively, with an overall consumption of ~38 mW at 1 V supply voltage. Baseband digital predistortion (DPD) could be studied further to improve ACLR, as it is widely used in literature to increase linearity and reduce spectral regrowth and unwanted emissions into

Fig. 17. Measured output spectrum: (a) LTE 10MHz; (b) LTE 20MHz.

| •                                            |                    |           | ` '                                  |                       |           |                                  |           |  |

|----------------------------------------------|--------------------|-----------|--------------------------------------|-----------------------|-----------|----------------------------------|-----------|--|

|                                              | [2]                |           | [4]                                  | [5]                   |           | This work                        |           |  |

| Architecture                                 | Quadrature<br>DRFC |           | 10b ΔΣ + Mismatch<br>Shaping 10b DAC | RQDAC + passive mixer |           | Digital Mixer +<br>SC RF FIR-DAC |           |  |

| Carrier Frequency<br>[MHz]                   | 800                |           | 900                                  | 900                   | 900 2400  |                                  | 900       |  |

| Supply voltage [V]<br>Output stage / Digital | 1.1 / 1.1          |           | 1.5 / 0.9                            | 0.9 / 1.1             |           | 1/1                              |           |  |

| DAC Resolution<br>[bits]                     | 6<br>(physical)    |           | 10<br>(physical)                     | 12<br>(physical)      |           | 1<br>(10 ENOB)                   |           |  |

| Peak P <sub>out</sub> [dBm]                  | 13.9               |           | 1.2                                  | 3.5                   |           | 4.6                              |           |  |

| LO feedthrough<br>[dBc]                      | -                  |           | -61                                  | < -57                 |           | -59                              |           |  |

| lmage [dBc]                                  | -                  |           | -36                                  | < -42                 |           | -60                              |           |  |

| CIM3 [dBc]                                   | -                  |           | -67                                  | < -50                 |           | -49                              |           |  |

| Modulation signal                            | LTE10              |           | LTE20                                | 20MHz                 |           | LTE20                            |           |  |

| Average P <sub>out</sub> [dBm]               | 6.97               |           | 0.9                                  | -3.5                  |           | -1.5                             |           |  |

| ACLR [dBc]                                   | -32.4 / -34.9      |           | -60.7 / -61.6                        | -42 / -59             | -47 / -59 | -34 / -43                        |           |  |

| Consumption [mW]                             | cw                 | LTE       | LTE                                  | 20MHz                 | 20MHz     | cw                               | LTE       |  |

| Output stage<br>Digital                      | 60.7               | 17.1<br>- | 75<br>22 (w/o DSM)                   | 11.1                  | 24.8      | 12.3<br>26                       | 8.8<br>29 |  |

| Active area [mm²]                            | 0.24               |           | 0.82                                 | 0.22                  |           | 0.047                            |           |  |

| Matching network                             | On PCB             |           | On-Chip                              | On PCB                |           | On BGA                           |           |  |

| Technology                                   | 28nm               |           | 28nm                                 | 28nm                  |           | 28nm FD-SOI                      |           |  |

Fig. 18. Performance summary and comparison with state-of-the-art.

adjacent bands [24]. Still, the DPD implementation would add extra cost in surface and power consumption for the dynamic correction feedback loop. Further description and comparison of existing DPD models can be found in [25].

The noise floor measured in a 3 MHz bandwidth is lower than -125 dBm/Hz at 200 MHz offset frequency, when transmitting both single-tone and LTE signals at the center frequency  $f_c = 900$  MHz, and showed no dependency on the

input signal amplitude. In addition, digital replicas appear at  $f_c \pm f_c/2$ , due to baseband sampling at  $f_{data} = f_c/2$ . The 28nm FD-SOI transmit chain performance is summarized and further compared with digital-intensive architectures in the same technology node (Fig. 18). In [2], a 6-bit switched-capacitor quadrature DRFC takes advantage of improved switching efficiency by disabling opposite cells. Next, mismatch shaping (MS) is introduced in [4] to minimize DAC static mismatch effects and reduce OOB noise by scrambling the order of conversion cells at each sampling instant. Furthermore, [5] describes a 12-bit incremental-charge based scheme to minimize dissipated power, while driving a 50  $\Omega$  load at 3.5 dBm peak output power.

The proposed digital transmit chain based on single-bit switched-capacitor RF FIR-DAC is very scalable, and the occupied silicon area can be drastically reduced, thanks to the tolerable mismatch of the unit cells. The total active area is 4 times smaller than the smallest previous design. The LO and image rejections compare favorably thanks to the body-bias-based duty-cycle correction, whereas the measured CIM3 is close to -50dBc. Delivering similar output power levels, the output stage of our system consumes less than [4] and [5], while the power consumption of the digital part is similar to [4]. Nevertheless, since the measured ACLR values are lower than in the two other designs, additional digital linearization techniques would be required, and add to the power consumption and area of the system.

Finally, the present FIR-DAC architecture is compatible with the PA design features detailed in [12], such as stacked transistors operating at twice the supply voltage, power combining, and on-chip matching to a very low output resistance  $\sim 3~\Omega$ , and could achieve an output power level enabling operation as stand-alone 5G LTE-M compliant power amplifier. With a modest amount of additional circuitry, the Delta-Sigma modulators and FIR transfer function could also be reconfigured for different resolution and bandwidth requirements. As shown in [14] and [15], up to 160MHz of signal bandwidth is achievable for 802.11 specifications by a DSM associated to a FIR-DAC of similar complexity to the one described in this paper.

#### V. CONCLUSIONS

The present paper describes the system-level design of an all-digital transmitter based on a hybrid architecture, combining single-bit DAC stages in a 109-tap FIR filter, and the integration of the RF FIR-DAC output stage in 28nm CMOS FD-SOI. The general idea behind this concept is to rely only on basic circuit elements, inverters and capacitors, arranged in a straightforward matrix of unit cells, with only one cell to develop, in addition to digital library cells. Still, maintaining the output power level at low supply voltages requires the use of lower load resistances, which raises additional issues in terms of interfacing the circuit to the antenna.

The single-bit core digital transmitter offers an attractive

alternative to both traditional design based on highresolution DAC architectures, and digital-intensive transmitters up to date, by shifting analog processing towards the digital domain, and pushing the digital domain up to the antenna. The true digital nature of the proposed solution provides extensive design space for digital processing enhancement towards flexible software defined radio, making this architecture an ideal candidate for next generation IoT devices.

#### REFERENCES

- [1] H. Song, R. Gharpurey, "Digitally Intensive Transmitter Employing RF Pulse Width Modulation for IoT Applications," *IEEE RFIC*, pp. 151–154, May 2015.

- [2] H. Jin, D. Kim, B. Kim, "Efficient digital quadrature transmitter based on IQ cell sharing," *IEEE J. Solid-State Circuits*, vol. 52, no. 5, pp. 1345-1357, May 2017.

- [3] H. Wang, et al., "A Highly-Efficient Multi-Band Multi-Mode All-Digital Quadrature Transmitter," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 61, no. 5, pp. 1321-1330, May 2014.

- [4] E. Roverato *et al.*, "All-Digital LTE SAW-Less Transmitter With DSP-Based Programming of RX-Band Noise," *IEEE J. Solid-State Circuits*, vol. 52, no. 12, pp. 3434-3445, Dec. 2017.

- [5] P.E. Paro Filho, M. Ingels, P. Wambacq, J. Craninckx, "A 0.22mm2 CMOS resistive charge-based direct-launch digital transmitter with -159dBc/Hz out-of-band noise," *IEEE ISSCC*, pp. 250–252, Feb. 2016.

- [6] R. Hezar, L. Ding, A. Banerjee, J. Hur, B. Haroun, "A PWM Based Fully Integrated Digital Transmitter/PA for WLAN and LTE Applications," *IEEE J. Solid-State Circuits*, vol. 50, no. 5, pp. 1117-1125, May 2015.

- [7] A. Frappé, A. Flament, B. Stefanelli, A. Kaiser, A. Cathelin, "An All-Digital RF Signal Generator Using High-Speed ΔΣ Modulators," *IEEE J. Solid-State Circuits*, vol. 44, no. 10, pp. 2722-2732, Oct. 2009.

- [8] S. Yoo, et al., "A Class-G Switched-Capacitor RF Power Amplifier," IEEE J. Solid-State Circuits, vol. 48, no. 5, pp. 1212-1224, May 2013.

- [9] M.-A. Dubois, et al., "Monolithic Above-IC Resonator Technology for Integrated Architectures in Mobile and Wireless Communication," *IEEE J. Solid-State Circuits*, vol. 41, no. 1, pp. 7-16, Jan. 2006.

- [10] A. Pozsgay, T. Zounes, R. Hossain, M. Boulemnakher, V. Knopik, S. Grange, "A Fully Digital 65nm CMOS Transmitter for the 2.4-to-2.7GHz WiFi/WiMAX Bands using 5.4GHz ΔΣ RF DACs," *IEEE ISSCC*, pp. 360-361, Feb. 2008.

- [11] A. Flament, A. Frappé, A. Kaiser, B. Stefanelli, A. Cathelin, H. Ezzeddine, "A 1.2 GHz semi-digital reconfigurable FIR bandpass filter with passive power combiner," *IEEE ESSCIRC*, pp. 418–421, Sept. 2008

- [12] R. Bhat, J. Zhou, H. Krishnaswamy, "A >1W 2.2GHz Switched-Capacitor Digital Power Amplifier with Wideband Mixed-Domain Multi-Tap FIR Filtering of OOB Noise Floor," *IEEE ISSCC*, pp. 234–235, Feb. 2017.

- [13] S. M. Taleie, T. Copani, B. Bakkaloglu, S. Kiaei, "A Bandpass  $\Delta\Sigma$  RF-DAC with Embedded FIR Reconstruction Filter," *IEEE ISSCC*, pp. 2370–2379, Feb. 2006.

- [14] F. T. Gebreyohannes, A. Frappé, A. Kaiser, "A Configurable Transmitter Architecture for IEEE 802.11ac and 802.11ad Standards," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 63, no. 1, pp. 9-13, Jan. 2016.

- [15] R.-C. Marin, A. Frappé, A. Kaiser, A. Cathelin, "Considerations for high-speed configurable-bandwidth time-interleaved digital deltasigma modulators and synthesis in 28 nm UTBB FDSOI," *IEEE NEWCAS*, pp. 1–4, June 2015.

- [16] S. Yoo, J. S. Walling, E. C. Woo, B. Jann, D. J. Allstot, "A Switched-Capacitor RF Power Amplifier," *IEEE J. Solid-State Circuits*, vol. 46, no. 12, pp. 2977-2987, Dec. 2011.

- [17] L. Ye, J. Chen, L. Kong, E. Alon, A. M. Niknejad, "Design Considerations for a Direct Digitally Modulated WLAN Transmitter

- With Integrated Phase Path and Dynamic Impedance Modulation," *IEEE J. Solid-State Circuits*, vol. 48, no. 12, pp. 3160-3177, Dec. 2013

- [18] A. V. Oppenheim, R. W. Schafer, and J. R. Buck, Discrete-Time Signal Processing, 2nd ed. Upper Saddle River, NJ, USA: Prentice Hall, pp. 465–472, 1999.

- [19] M. S. Alavi, R. B. Staszewski, L. C. N. de Vreede, J. R. Long, "A Wideband 2times 13-bit All-Digital I/Q RF-DAC," *IEEE Trans. Microw. Theory Techn.*, vol. 62, no. 4, pp. 732-752, Apr. 2014.

- [20] R. Bhat and H. Krishnaswamy, "Design Tradeoffs and Predistorion of Digital Cartesian RF-Power-DAC Transmitters," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 63, no. 11, pp. 1039-1043, Nov. 2016.

- [21] A. Cathelin, "Fully Depleted Silicon on Insulator Devices CMOS: The 28-nm Node Is the Perfect Technology for Analog, RF, mmW, and Mixed-Signal System-on-Chip Integration," *IEEE Solid State Circuits Mag.*, vol. 9, no. 4, pp. 18-26, Nov. 2017.

- [22] Y.-H Chen, N. Fong, B. Xu, C. Wang, "An LTE SAW-less transmitter using 33% duty-cycle LO signals for harmonic suppression," *IEEE ISSCC*, pp. 1-3, Feb. 2015.

- [23] V. Bhagavatula, *et al.*, "A SAW-less reconfigurable multimode transmitter with a voltage-mode harmonic-reject mixer in 14nm FinFET CMOS," *IEEE ISSCC*, pp. 220–221, Feb. 2017.

- [24] W. M. Gaber, P. Wambacq, J. Craninckx, M. Ingels, "A 21-dBm I/Q Digital Transmitter Using Stacked Output Stage in 28-nm Bulk CMOS Technology," *IEEE Trans. Microw. Theory Techn.*, vol. 65, no. 11, pp. 4744-4756, Nov. 2017.

- [25] G. Xu, T. Liu, Y. Ye, T. Xu, H. Wen, and X. Zhang, "Generalized Two-Box Cascaded Nonlinear Behavioral Model for Radio Frequency Power Amplifiers with Strong Memory Effects," *IEEE Trans. Microw. Theory Techn.*, vol. 62, no. 12, pp. 2888-2899, Dec. 2014.

**Răzvan-Cristian Marin** (S'14-M'17) received the B.Sc. and M.Sc. degrees in electronics and electrical engineering from the University "Politehnica" Bucharest, Romania in 2011 and 2013, respectively. 2017 he received the Ph.D. degree from the University of Lille, France. He was with the Silicon

Microelectronics group at IEMN (Institut d'Electronique, de Microelectronique et des Nanotechnologies) in Villeneuve d'Ascq, France (2013-2018). He recently joined Ericsson Research in Lund, Sweden. His current research activity concentrates on RF front-end architectures and mixed-signal design for RF communication systems.

Antoine Frappé (M'08-SM'17) received the M.Sc. and Ph.D. degree in electrical engineering from the University of Science and Technology, Lille, France in 2004 and 2007. He also graduated from ISEN Lille engineering school in 2004. He received a Fulbright grant in 2008 to pursue research in communication

systems at the Berkeley Wireless Research Center (BWRC) at UC Berkeley, CA. He is now Associate Professor at ISEN Lille – Yncréa Hauts-de-France. His current research interests include digital RF transmitters, mixed-signal design for RF and mmW communication systems and continuous-time digital signal processing for smart sensors. He received the Best Student Paper Award of the 2011 Symposium on VLSI Circuits.

Bruno Stefanelli (S'86–M'87) received the engineering diploma from the Institut Supérieur d'Electronique du Nord (ISEN), Lille, France, in 1986. In 1992, he received the Ph.D. degree from the University of Lille. In 1992, he joined the analog/RF IC design group at the Institut d'Electronique, de Microelectro-

nique et de Nanotechnologies (IEMN) in Villeneuved'Ascq where he worked on continuous and discrete time analog circuits, data-converters and RF-MEMS. His present research activities concern RF and millimeter wave circuits for telecommunications. He is also a Professor at ISEN.

Philippe Cathelin received the microelectronics engineer degree from the Ecole Superieure d'Ingenieurs en Electrotechnique et Electronique (ESIEE), Marne-La Vallee, France, in 1989. He first joined MS2 (Mixed Silicon Structures), Roubaix, France, working on low power low voltage

communication circuits. Starting from 1997, with the wireless division of ST Microelectronics, Grenoble, France, he designed RF BiCMOS transmitters for different cellular standards before joining, in 2005, ST-Ericsson, Crolles, France, implementing RF transceivers in CMOS. He is currently back to ST, since 2012, in the R&D organization involved in advanced CMOS mmW design activities.

Andreia Cathelin (M'04, SM'11) started electrical engineering at the Polytechnic Institute of Bucarest, Romania and graduated from ISEN Lille, France in 1994. In 1998 and 2013 respectively, she received PhD and "habilitation à diriger des recherches"

(French highest academic degree) from the Université de Lille 1, France. Since 1998, she has been with STMicroelectronics (STM), Crolles, France, now Fellow in Digital Front-End Manufacturing & Technology. Her focus areas are in the design of advanced RF/mmW/THz and ultra-low-power circuits and systems. Andreia has had numerous responsibilities inside IEEE since more than 15 years: at ISSCC, VLSI Symposium and ESSCIRC for TPC and Executive/Steering Committees respectively, and has been SSCS elected Adcom member 2015 to 2017. Andreia is a co-recipient of the ISSCC 2012 Jan Van Vessem Award and of the ISSCC 2013 Jack Kilby Award and the winner of the 2012 STM Technology Council Innovation Prize, for having introduced on the company's roadmap the integrated CMOS THz technology for imaging applications.

Andreas Kaiser received the Engineering diploma from the Institut Supérieur d'Electronique du Nord (ISEN), Lille, France, in 1984, and the PhD degree in 1990 from the University of Lille. In 1990 he joined the Centre National de la

©IEEE Version submitted for final publication in

Recherche Scientifique (CNRS) where he was responsible for the analog/RF IC design group at the Institut d'Electronique, de Microelectronique et de Nanotechnologies (IEMN) in Lille. He is currently vice-president for research and innovation at the Yncrea Engineering Graduate School. His research interests are continuous and discrete time analog circuits, data-converters, analogue design automation, RF-MEMS and RF circuits. Prof. Kaiser served as TPC Chair of the European Solid State Circuits Conference in 1995 and 2005 and has been a guest and associate editor to the IEEE Journal of Solid State Circuits.