### Parallel Branch-and-Bound revisited for solving permutation combinatorial optimization problems on multi-core processors and coprocessors

Rudi Leroy

#### ▶ To cite this version:

Rudi Leroy. Parallel Branch-and-Bound revisited for solving permutation combinatorial optimization problems on multi-core processors and coprocessors. Distributed, Parallel, and Cluster Computing [cs.DC]. Université Lille 1, 2015. English. NNT: . tel-01248563

#### HAL Id: tel-01248563 https://inria.hal.science/tel-01248563

Submitted on 27 Dec 2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Ecole Doctorale Sciences Pour l'Ingénieur Université Lille 1 Nord-de-France Centre de Recherche en Informatique, Signal et Automatique de Lille (UMR CNRS 9189) Centre de Recherche INRIA Lille Nord Europe

Thèse présentée pour obtenir le grade de docteur Discipline : Informatique

# Parallel Branch-and-Bound revisited for solving permutation combinatorial optimization problems on multi-core processors and coprocessors.

Défendue par :

#### **Rudi Leroy**

Novembre 2012 - Novembre 2015

Devant le jury composé de:

Rapporteur : Catherine Roucairol, Professeur, Université de Versailles

Rapporteur : Pierre Sens, Professeur, Université Paris 6

Examinateur : Matthieu Basseur, Maître de Conférences HDR, Université d'Angers

Examinateur : Michel Kern, Chargé de Recherche, Inria Rocquencourt

Directeur de thèse : Nouredine Melab, Professeur, Université de Lille 1

Co-encadrant : Mohand Mezmaz, Chargé de Recherche, Université de Mons

Invité : Daniel Tuyttens, Professeur, Université de Mons

Numéro d'ordre: 41840 | Année: 2015

#### **Abstract**

Solving large permutation Combinatorial Optimization Problems (COPs) using Branch-and-Bound (B&B) algorithms results in the generation of a very large pool of subproblems. Therefore, defining a dedicated data structure is crucial to store and manage efficiently that pool. In this Ph.D thesis, we propose an original data structure called Integer-Vector-Matrix (IVM) for permutation COPs based on the factorial number system. Consequently, we redefine the operators of the B&B algorithm acting on it. For performance evaluation in terms of memory footprint and CPU time usage, we conduct a complexity analysis and an extensive experimentation using the permutation Flow-Shop Scheduling Problem (FSP) as a case study. The deque data structure referred to as LL is considered in our work as a basis for comparison with IVM. Compared to LL, IVM requires up to n less memory than LL, n being the size of permutations. Moreover, the IVM-based B&B is up to one order of magnitude faster than its LL-based counterpart in managing the pool of subproblems. Another advantage of IVM over LL is that its memory requirement is constant and predictable.

On the other hand, according to the Top500 international ranking the tendency of HPC technologies is to use multi-core processors and many-core accelerators/coprocessors as key-building blocks. Another contribution of this thesis is to revisit parallel B&B for multi-core processors, GPU accelerators and MIC coprocessors using IVM and LL. As the tree explored by a B&B applied to FSP is highly irregular in shape and size, the thread-based Work Stealing (WS) paradigm is used for parallelization on multi-core processors. Unlike most related works that use concurrent data structures, we propose a private IVM-based and LL-based WS mechanism. In addition, work units are coded in a coalesced thus optimized way using factoradic-based intervals. We also investigate five different WS strategies. Extensive experiments show that in overall IVM outperforms LL in memory footprint and CPU time usage whatever is the used WS strategy. For the many-core parallelization, the proposed approach consists in performing the branching and bounding operators on the coprocessor. Such approach raises some issues, addressed in this thesis, mainly thread mapping, thread/branch divergence and data placement optimization on GPU, and vectorization on Intel Xeon Phi. An extensive experimental study shows that IVM is particularly more efficient than LL within the many-core context. Moreover, even with vectorization (of the lower bound), which allows a significant performance improvement on Intel Xeon Phi, the GPU-based approach is faster. Finally, the many-core approaches are faster than their multi-core counterpart by one order of magnitude.

**Keywords:** Branch-and-Bound, Multi-core, Many-core (GPU, MIC), Permutation optimization problems, Flow-Shop.

#### Résumé

La résolution de problèmes de permutation en optimisation combinatoire au moyen d'algorithmes Branch-and-Bound (B&B) génère un très grand pool de sous-problèmes. Par conséquent, la définition d'une structure de données dédiée est cruciale pour stocker et gérer efficacement ce pool. Dans cette thèse, nous proposons une structure de données originale appelée Integer-Vector-Matrix (IVM) pour les problèmes de permutation basée sur la numération factorielle. En conséquence, nous redéfinissons les opérateurs de l'algorithme B&B agissant sur celle-ci. Pour l'évaluation de performance en termes de consommation mémoire et d'utilisation du CPU, nous avons réalisé une analyse de complexité et une expérimentation intensive en utilisant le problème d'ordonnancement de type Flow-Shop (FSP) comme étude de cas. La structure de données *deque*, désignée par LL dans ce manuscrit, est utilisée comme base de comparaison pour évaluer la performance d'IVM. Par rapport à LL, IVM nécessite jusqu'à n fois moins de mémoire que LL, n étant la taille des permutations. En outre, B&B basé sur IVM est environ 10 fois plus rapide que son équivalent basé sur LL dans la gestion du pool de sous-problèmes. Un autre avantage d'IVM sur LL est que ses besoins en mémoire sont constants et prévisibles.

D'autre part, d'après le classement international Top500 la tendance des technologies HPC est d'utiliser des processeurs multi-coeurs et des accélérateurs/coprocesseurs comme des briques-clés pour la construction de machines. Une autre contribution de cette thèse est de revisiter l'algorithme B&B parallèle pour les processeurs multi-coeurs, les accélérateurs GPU et les coprocesseurs MIC en utilisant IVM et LL. Comme l'arbre exploré par un B&B appliqué au FSP est hautement irrégulier en forme et en taille, le paradigme de vol de cycles (WS) basé sur les threads est utilisé pour la parallélisation multi-coeur. Contrairement à la majorité des travaux existants, qui utilisent des structures de données concurrentes, nous proposons un mécanisme de WS utilisant des structures (IVM et LL) privées ou "distribuées". En outre, les unités de travail sont codées de manière compressée et donc optimisée en utilisant des intervalles de factorielles. Nous étudions également cinq stratégies de WS différentes. Une expérimentation intensive montre que globalement IVM est plus efficace que LL en termes d'empreinte mémoire et d'utilisation du temps CPU et ce quel que soit la stratégie WS utilisée. Pour la parallélisation multi-coeur, l'approche proposée consiste à effectuer le branchement et l'évaluation des bornes sur le coprocesseur.

Cette approche soulève des problèmes, adressés dans cette thèse, notamment le mapping de threads, la divergence de branches/threads et l'optimisation du placement des données sur GPU, et la vectorisation sur Intel Xeon Phi. Une étude expérimentale montre qu'IVM est particulièrement plus efficace que LL dans le contexte many-core. En outre, même avec la vectorisation (de la borne inférieure), ce qui permet une amélioration significative des performances sur les processeurs Intel Xeon Phi, l'approche sur GPU est plus rapide. Enfin, les approches many-core sont environ 10 fois plus rapides que leurs homologues multi-core.

**Mots clés:** Branch-and-Bound, Multi-coeur, Many-core (GPU, MIC), Problèmes de permutation, Flow-Shop.

## Acknowledgments

## **List of Figures**

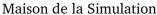

| 2.1  | Illustration of a permutation FSP where $n=3$ and $m=4$ . The table shows     |    |

|------|-------------------------------------------------------------------------------|----|

|      | the processing times of the jobs on each machine. The Gantt diagram shows     |    |

|      | the optimal solution for this particular instance                             | 13 |

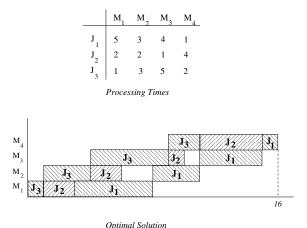

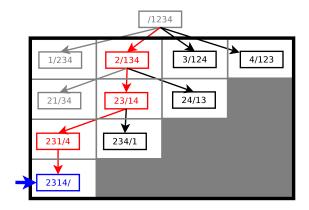

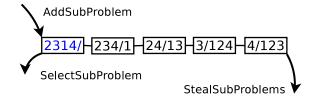

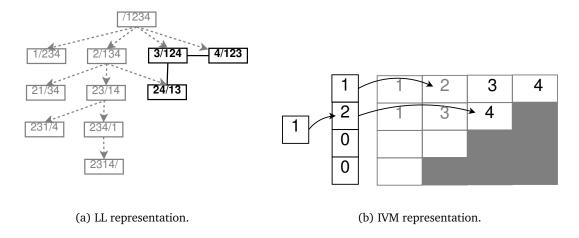

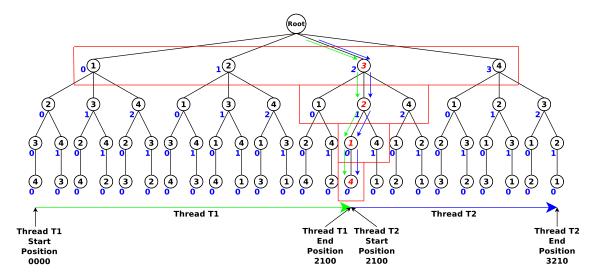

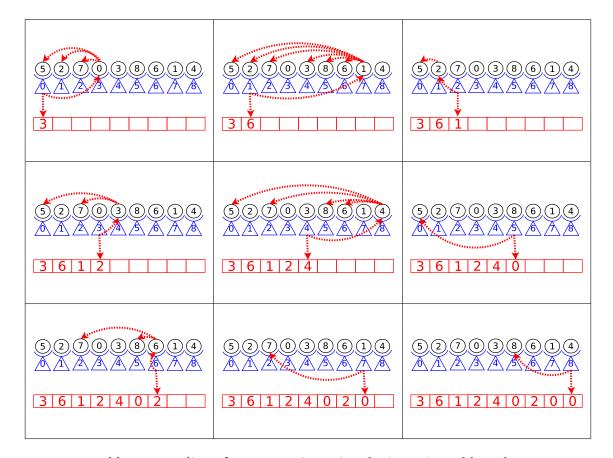

| 3.1  | An example of a pool obtained when solving a permutation problem of size 4.   | 34 |

| 3.2  | LL-based (or deque-based) representation of a pool of subproblems             | 36 |

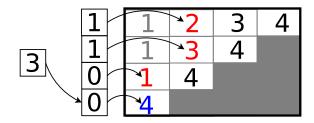

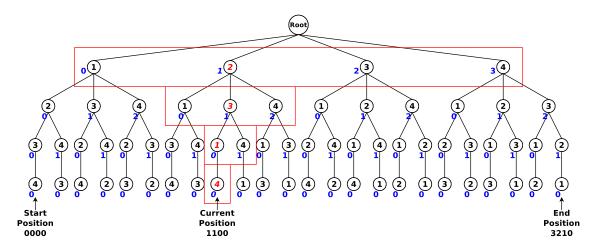

| 3.3  | IVM representation of a pool of subproblems                                   | 40 |

| 3.4  | Representation of the IVM data structure within the context of the whole      |    |

|      | tree                                                                          | 42 |

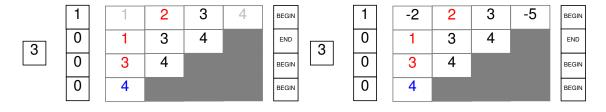

| 3.5  | IVM representation of a pool of subproblems with a direction vector           | 43 |

| 3.6  | IVM representation of eliminated subproblems                                  | 43 |

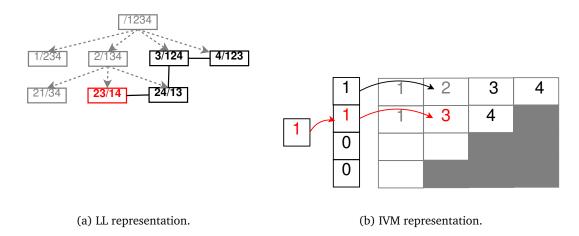

| 3.7  | Selection Operator                                                            | 44 |

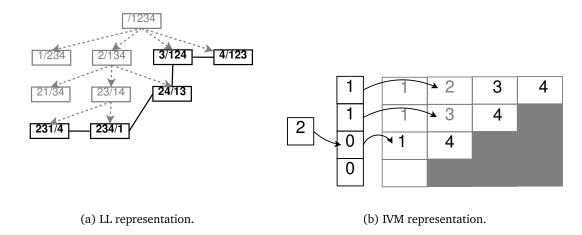

| 3.8  | Branching Operator                                                            | 45 |

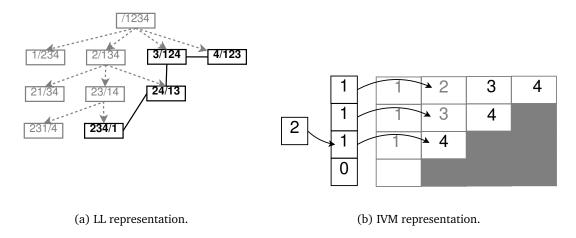

| 3.9  | Elimination Operator when the subproblem is not the last of its row           | 47 |

| 3.10 | Elimination Operator when the subproblem is the last of its row               | 47 |

| 4.1  | Illustration of the multi-parametric parallel model                           | 57 |

| 4.2  | Illustration of the parallel evaluation of bounds model                       | 57 |

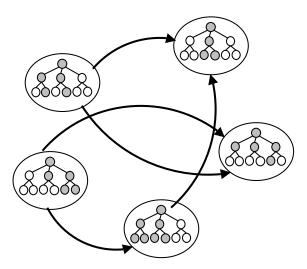

| 4.3  | Illustration of the parallel tree exploration model                           | 59 |

| 4.4  | IVM representation of a pool of subproblems                                   | 61 |

| 4.5  | Representation of an interval division at an arbitrary point                  | 65 |

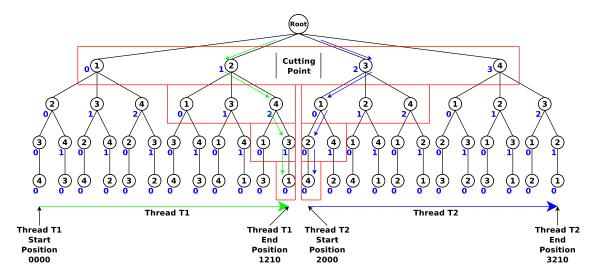

| 4.6  | Representation of an interval division at a point chosen to avoid redundancy. | 66 |

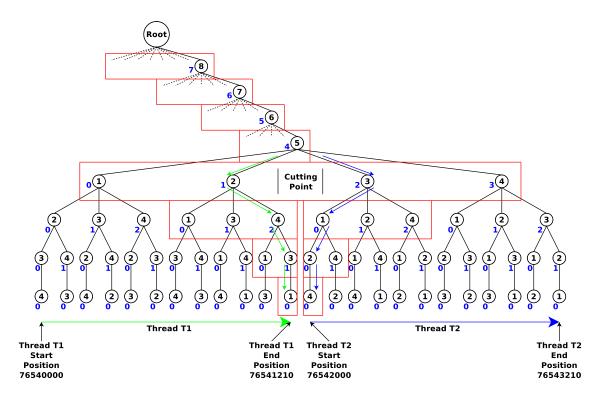

| 4.7  | Representation of a generalization of an interval division between subtrees.  | 68 |

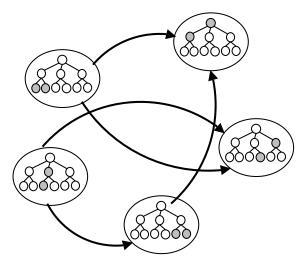

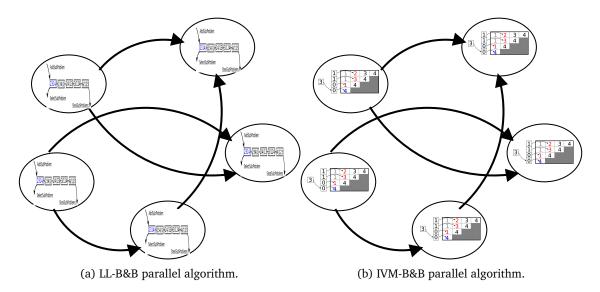

| 4.8  | Illustration of the LL-B&B and a IVM-B&B parallel algorithms using the        |    |

|      | same work stealing strategy                                                   | 70 |

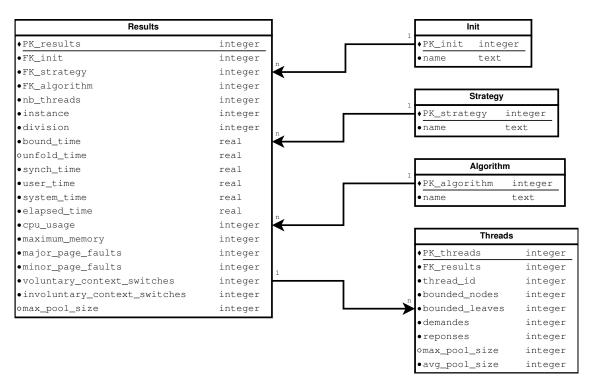

| 4.9  | Entity-relationship model of the database containing the results of the ex-   |    |

|      | periments                                                                     | 74 |

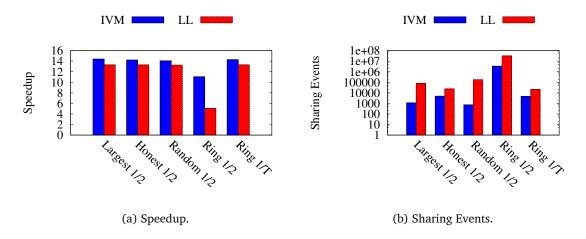

| 4.10 | Comparison of speedup and sharing events for 20 jobs on 20 machines for       |    |

|      | IVM and LL                                                                    | 76 |

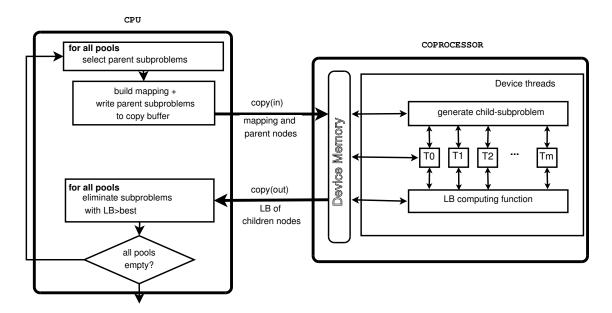

| 5.1  | Coprocessor-based B&B                                                         | 83 |

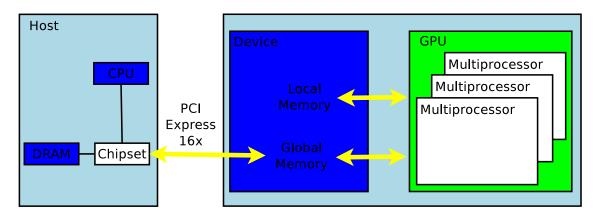

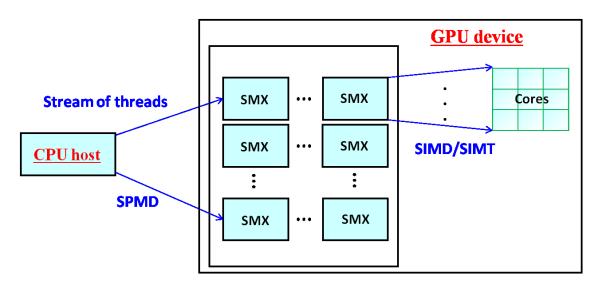

| 5.2  | Hardware view: GPU = coprocessor of CPU                                       | 85 |

| 5.3  | Software view: Parallel program = weakly parallel/serial host code + mas-     |    |

|      | sively parallel device code                                                   | 85 |

vi List of Figures

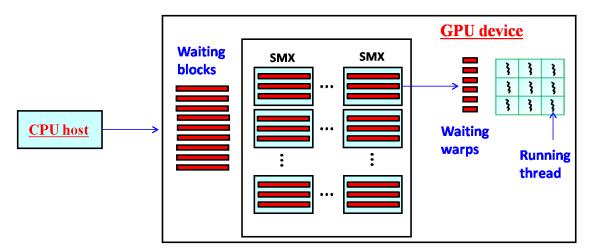

| 5.4 | Software view: Parallel program = grid(s) of block(s) of threads executed |    |

|-----|---------------------------------------------------------------------------|----|

|     | as warps of 32 threads                                                    | 86 |

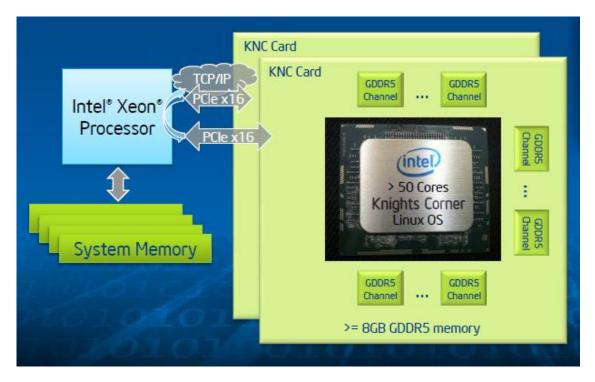

| 5.5 | Hardware view: Intel Xeon Phi = coprocessor of CPU                        | 89 |

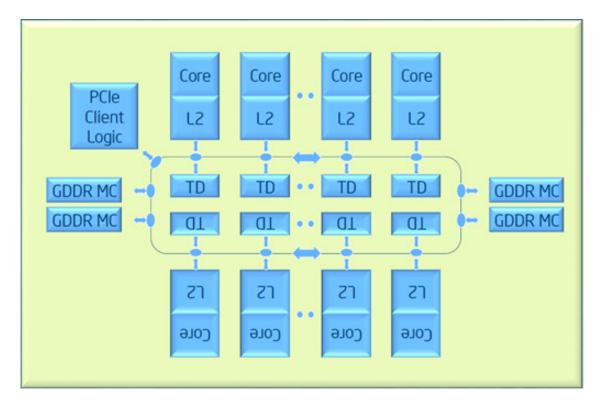

| 5.6 | Hardware view: Knights Corner core                                        | 90 |

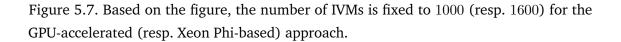

| 5.7 | Elapsed time vs. Number of IVMs                                           | 94 |

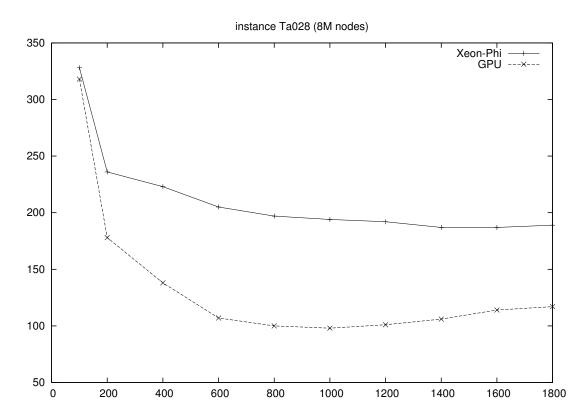

| 5.8 | Comparison between the linked-list and IVM-based B&B in terms of elapsed  |    |

|     | CPU time when solving instance 30 using different number of hardware      |    |

|     | threads                                                                   | 97 |

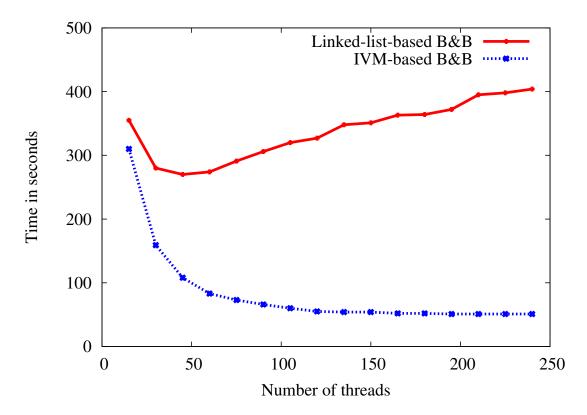

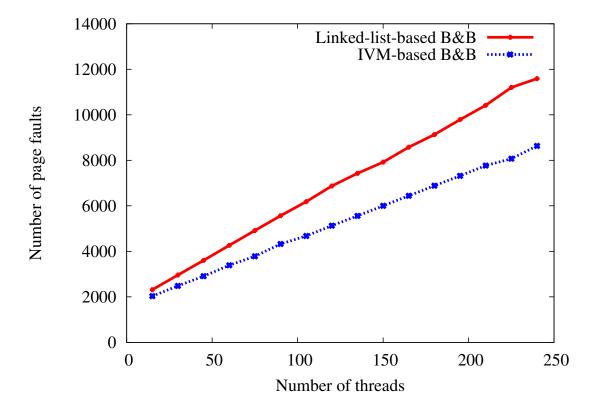

| 5.9 | Comparison between the linked-list and the IVM-based B&B in terms of the  |    |

|     | number page faults when solving instance 30 using different number of     |    |

|     | hardware threads.                                                         | 99 |

## **List of Tables**

| 2.1 | Roman digits and their values                                                                                                                 | 14         |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 2.2 | Factorial system and its radixes, place-values and digits for the seven first                                                                 |            |

|     | positions                                                                                                                                     | 17         |

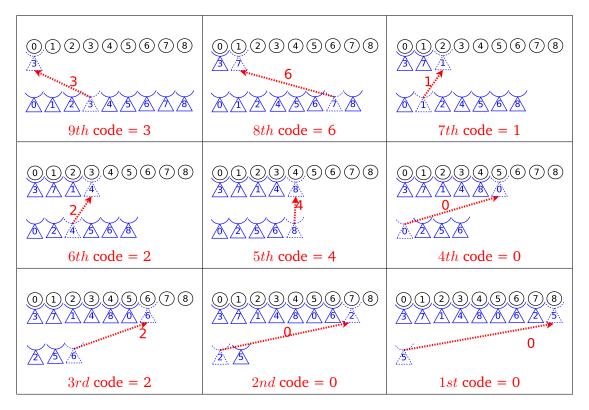

| 2.3 | Encoding a permutation using a Lehmer code                                                                                                    | 27         |

| 2.4 | Decoding a permutation represented by a Lehmer code                                                                                           | 28         |

| 3.1 | Comparison of serial IVM and LL B&B algorithms in terms of maximum memory                                                                     | 49         |

| 3.2 | Comparison of the size of IVM and the average size of LL when solving the                                                                     | <b>5</b> 0 |

| 3.3 | ten instances defined with 20 jobs                                                                                                            | 50         |

| 3.4 | ten instances defined with 50 jobs                                                                                                            | 50         |

|     | CPU time used for the management of the pool when solving the instances defined with 20 jobs                                                  | 52         |

| 3.5 | Comparison of serial IVM and LL-based B&B algorithms in terms of the CPU time used for the management of the pool when solving the instances  |            |

|     | defined with 50 jobs                                                                                                                          | 52         |

| 4.1 | Number of explored subproblems for 20x20 instances when initialized with the optimal solution                                                 | 73         |

| 4.2 | Number of explored subproblems for 50x10 instances when initialized with                                                                      | / 3        |

| 4.0 | the optimal solution                                                                                                                          | 73         |

| 4.3 | Comparison of IVM-B&B and LL-B&B with 16 threads for 20 jobs on 20 machines with an initialization to optimum in terms of speedup and sharing |            |

|     | events                                                                                                                                        | 76         |

| 4.4 | Comparison of IVM-B&B and LL-B&B with 16 threads for 20 jobs on 20 machines in terms of memory usage                                          | 78         |

| 4.5 | Comparison of IVM-B&B and LL-B&B with 16 threads for 20 jobs on 20                                                                            |            |

|     | machines in terms of CPU Time                                                                                                                 | 79         |

| 5.1 | Hardware execution platform                                                                                                                   | 93         |

| 5.2 | Exploration time (in seconds) for solving Flow-Shop instances <i>Ta021-Ta030</i> initialized at optimal solution                              | 95         |

viii List of Tables

| 5.3 | 1                                                                        | 00  |

|-----|--------------------------------------------------------------------------|-----|

|     | elapsed CPU time when solving instances with 240 threads                 | 98  |

| A.1 | Comparison of serial IVM-B&B and LL-B&B when the solution is initialized |     |

|     | to optimum in terms of memory.                                           | 113 |

| A.2 | Comparison of serial IVM-B&B and LL-B&B when the solution is initialized |     |

|     | to optimum in terms of memory.                                           | 113 |

| A.3 | Comparison of serial IVM-B&B and LL-B&B when the solution is initialized |     |

|     | to optimum in terms of CPU Time                                          | 114 |

| A.4 | Comparison of serial IVM-B&B and LL-B&B when the solution is initialized |     |

|     | to optimum in terms of CPU Time                                          | 114 |

| A.5 | Comparison of serial IVM-B&B and LL-B&B when the solution is initialized |     |

|     | to infinity in terms of CPU Time                                         | 115 |

| A.6 | Comparison of serial IVM-B&B and LL-B&B when the solution is initialized |     |

|     | to optimum in terms of CPU Time                                          | 115 |

| B.1 | Coding of a permutation using the inversion table code                   | 118 |

| B.2 | Decoding a permutation represented by a code obtained with the inversion |     |

|     | table.                                                                   | 120 |

## **Contents**

| 1 | Intr | oductio | on                                      | 1  |

|---|------|---------|-----------------------------------------|----|

| 2 | Perr | nutatio | on-based optimization problems          | 7  |

|   | 2.1  | Introd  | luction                                 | 7  |

|   | 2.2  | Permu   | ntation optimization problems           | 8  |

|   |      | 2.2.1   | Traveling-salesman problem              | 8  |

|   |      | 2.2.2   | Quadratic assignment problem            | 9  |

|   |      | 2.2.3   | Job-Shop problem                        | 11 |

|   |      | 2.2.4   | Permutation Flow-Shop problem           | 11 |

|   | 2.3  | Factor  | ial number system                       | 12 |

|   |      | 2.3.1   | Definition of number system             | 13 |

|   |      | 2.3.2   | Definition of factorial number system   | 16 |

|   |      | 2.3.3   | Operations based on decimal system      | 17 |

|   |      | 2.3.4   | Operations based on factorial system    | 20 |

|   | 2.4  | Handl   | ing permutations with factorial numbers | 22 |

|   |      | 2.4.1   | Basic concepts                          | 22 |

|   |      | 2.4.2   | Permutation to factorial number         | 25 |

|   |      | 2.4.3   | Factorial number to permutation         | 27 |

|   | 2.5  | Concl   | usion                                   | 29 |

| 3 | Seri | al IVM  | -based B&B                              | 31 |

|   | 3.1  | Introd  | luction                                 | 31 |

|   | 3.2  | Conve   | entional serial B&B                     | 32 |

|   |      | 3.2.1   | Algorithm description                   | 32 |

|   |      | 3.2.2   | LL data structure                       | 35 |

|   |      | 3.2.3   | B&B operators                           | 37 |

|   | 3.3  | IVM-b   | ased serial B&B                         | 39 |

|   |      | 3.3.1   | IVM data structure                      | 40 |

|   |      | 3.3.2   | IVM advanced techniques                 | 42 |

|   |      | 3.3.3   | Revisited B&B operators                 | 44 |

|   | 3.4  | Experi  | imentation                              | 46 |

|   |      | 3.4.1   | Experimental settings                   | 46 |

|   |      | 3.4.2   | Memory evaluation                       | 48 |

|   |      | 3.4.3   | CPU Time evaluation                     | 51 |

| x | Contents |

|---|----------|

|   |          |

| Bil | Bibliography 105 |                                                           |     |  |  |  |  |

|-----|------------------|-----------------------------------------------------------|-----|--|--|--|--|

| 6   | Con              | clusions and perspectives                                 | 101 |  |  |  |  |

|     | 5.6              | Conclusion                                                | 96  |  |  |  |  |

|     |                  | 5.5.2 Experimental results                                | 94  |  |  |  |  |

|     |                  | 5.5.1 Hardware and software testbed and parameter setting | 93  |  |  |  |  |

|     | 5.5              | Experimentation                                           | 92  |  |  |  |  |

|     |                  | 5.4.2 Parallelization of B&B for Intel Xeon Phi           | 91  |  |  |  |  |

|     |                  | 5.4.1 Parallelization on Intel Xeon Phi                   | 88  |  |  |  |  |

|     | 5.4              | MIC-based implementation of B&B                           | 88  |  |  |  |  |

|     |                  | 5.3.2 Parallelization of B&B for GPU                      | 86  |  |  |  |  |

|     |                  | 5.3.1 Parallelization on GPU                              | 84  |  |  |  |  |

|     | 5.3              | GPU-based implementation of B&B                           | 84  |  |  |  |  |

|     | 5.2              | Coprocessor-accelerated B&B: the general design           | 82  |  |  |  |  |

|     | 5.1              | Introduction                                              | 81  |  |  |  |  |

| 5   | Man              | y-core IVM-based B&B                                      | 81  |  |  |  |  |

|     | 4.5              | Conclusion                                                | 80  |  |  |  |  |

|     |                  | 4.4.4 CPU time evaluation                                 | 78  |  |  |  |  |

|     |                  | 4.4.3 Memory evaluation                                   | 77  |  |  |  |  |

|     |                  | 4.4.2 Strategy and granularity policies evaluation        | 75  |  |  |  |  |

|     |                  | 4.4.1 Experimental settings                               | 72  |  |  |  |  |

|     | 4.4              | Experimentation                                           | 72  |  |  |  |  |

|     |                  | 4.3.4 Victim selection and granularity policies           | 67  |  |  |  |  |

|     |                  | 4.3.3 Dividing one factoradic interval into two intervals | 63  |  |  |  |  |

|     |                  | 4.3.2 Coalesced work units                                | 61  |  |  |  |  |

|     |                  | 4.3.1 WS-based B&B implementation                         | 59  |  |  |  |  |

|     | 4.3              | Work stealing strategies for multi-core IVM-based B&B     | 59  |  |  |  |  |

|     |                  | 4.2.4 Parallel tree exploration model                     | 58  |  |  |  |  |

|     |                  | 4.2.3 Parallel evaluation of a bound model                | 58  |  |  |  |  |

|     |                  | 4.2.2 Parallel evaluation of bounds model                 | 57  |  |  |  |  |

|     |                  | 4.2.1 Multi-parametric parallel model                     | 56  |  |  |  |  |

|     | 4.2              | Parallel models for B&B algorithms                        | 56  |  |  |  |  |

|     | 4.1              | Introduction                                              | 55  |  |  |  |  |

| 4   | Mul              | Multi-core IVM-based B&B 55                               |     |  |  |  |  |

|     | 3.5              | Conclusion                                                | 53  |  |  |  |  |

|     |                  |                                                           |     |  |  |  |  |

| Contents                     | xi  |

|------------------------------|-----|

| A Other experimental results | 113 |

| B Inversion table            | 117 |

xii Contents

## Introduction

The Ph.D thesis presented in this manuscript has been realized within the DOLPHIN <sup>1</sup> research group from Inria Lille-Nord Europe, CNRS/CRIStAL and Université Lille 1. The thesis has been funded by Inria and took place in the premises of Maison de la Simulation at Saclay.

In practice, many problems can be modeled as combinatorial optimization problems (COPs) which consist in maximizing or minimizing a cost function under some constraints. In this thesis, we focus on permutation-based COPs such as the Quadratic Assignment Problem (QAP), the Traveling Salesman Problem (TSP), the Flow-Shop problem, and so on. For those problems permutations are used to code/represent the candidate solutions. For instance, for a scheduling problem such as Flow-Shop the numbers of a permutation coding a given solution may designate jobs. For example, a solution coded as a permutation (3,4,2,1) means that the 4 jobs should be executed in the following order: job 3, then jobs 4 and 2, and finally job 1.

Solving permutation COPs consists in finding an optimal permutation among a large finite set of possible permutations. A wide range of these problems are known to be NP-hard. Therefore, metaheuristics are often used to solve them especially when the considered instances are very large [Mehdi 2011, Luong 2011]. Although these approximate methods allow to reduce the size of the explored search space and to speed up its exploration they fail in general to provide exact solutions. Conversely, exact optimization methods allow to find optimal solutions with proof of optimality. The branch-and-bound (B&B) algorithm is one of the most used exact methods to solve permutation COPs: QAP in [Mautor 1994a], TSP in [Carneiro 2011], Flow-Shop in [Melab 2012], and so on. This tree-based algorithm is based on an implicit enumeration of all the feasible solutions of the problem to be solved using four operators: branching, bounding, selection and pruning. It proceeds in several iterations during which it recursively decomposes the problem into subproblems and progressively improves the best solution found so far. The

<sup>&</sup>lt;sup>1</sup>Discrete multi-objective Optimization for Large-scale Problems with Hybrid dIstributed techNiques

pool of generated and not yet examined subproblems are kept into some data structure initialized to the original problem. The proposition of an efficient data structure, that is considered in this thesis, is one of the major challenging issues that should be addressed for an efficient implementation of B&B [Mans 2006]. At each iteration, a subproblem is selected from this data structure, according to some strategy (depth-first, best-first,...), using the selection operator. The branching operator performs its decomposition into other subproblems. The bounding operator calculates a lower bound of each generated subproblem. Each subproblem having a lower bound greater than the best solution found so far is discarded using the pruning operator.

The lower bound-based pruning mechanism is a key idea of the B&B algorithm that significantly reduces the number of explored nodes. However, B&B remains timeintensive when it comes to solve very large problem instances. Therefore, only small or moderately-sized instances are often solved in practice in a reasonable amount of time using a single processing core [Garey 1976]. For this reason, over the last decades, parallel computing has been revealed as an attractive way to deal with larger instances of COPs including permutation-based ones. The design and implementation of parallel B&B is strongly influenced by the target execution platform [Bader 2005]. To take into account the associated hardware characteristics, different parallelization approaches have been proposed in the past for Massively Parallel Processors (MPP) [Allen 1997], Networks or Clusters of Workstations [Quinn 1990, Dowaji 1995, Tschöke 1995] and Shared Memory or SMP machines [Mans 2006, Casado 2008]. Recently, the parallelization of B&B has been revisited for multi-core (clusters of) processors [Barreto 2010] and Graphics Processing Units (GPU) [Carneiro 2011, Lalami 2012] and their combination [Chakroun 2013a, Vu 2014]. MIC coprocessors are becoming more and more used in High Performance Computing and serious competitors of GPU accelerators. Indeed, the first ranked machine of Top500 (June 2015) includes Xeon Phi coprocessors. However, to the best of our knowledge the parallelization of B&B for MIC architectures has not yet been considered in the literature. In addition to multi-core and GPU accelerators, the parallelization of B&B on MIC coprocessors is also considered in this thesis.

On the other hand, the focus is put here on parallel B&B algorithms applied to permutation COPs. Without loss of generality, the Flow-Shop Scheduling Problem (FSP) is considered as a case study. The problem consists in scheduling a pool of jobs on a set of machines with respect to two constraints: the jobs are processed on all the machines in the same order and each machine cannot process more than one job at a time. The objective is to find a processing order on each machine such that the time required to complete all

jobs is minimized. The lower bound function considered in our work is that proposed by Johnson in [Johnson 1954] for two machines and generalized in [Lenstra 1978] to more than two machines. The overall major objective of this thesis is twofold: (1) proposing a new data structure for an efficient storage and management of the subproblems generated during the resolution of a permutation COP; (2) according to this new data structure, revisiting the design and implementation of serial and parallel B&B algorithms for multicore processors and coprocessors for solving challenging permutation COPs. Rethinking B&B algorithms for multi-core processors and coprocessors raises several design and implementation challenges. These challenges and associated contributions are summarized in the following:

As for other algorithms, data structures play a major role in the performance of a B&B algorithm [Mans 2006] and irregular applications in general [Acar 2013]. Indeed, the efficiency of its four operators depends strongly on the data structure they act on. Several abstract data structures have been proposed in the literature for B&B algorithms including priority queues for best-first B&B, stacks for depth-first B&B, and so on. Moreover, different implementations have been proposed for their efficient management. For instance, in [Mans 2006] two implementations of the priority queue have been investigated: a skew heap (self-adjusting form of heap) and funnel tree. More generally, efficient implementations of the priority queue are provided in programming languages such as C++ and Java. Another popular data structure provided in those languages is the double-ended queue (or deque). A deque is a sequence container with dynamic size that can be expanded or contracted on both ends (either its front or its back). This data structure is important and often used in the multi-core context using the work stealing mechanism in which stealing operations are performed from the back of the queue. This is why it is considered in our work as a basis for comparison with our new data structure. In the literature, deque is also called head-tail linked list. In the rest of this manuscript, it is abbreviated by LL which stands for Linked-List. LL is a generic data structure which makes it frequently used. However, we believe that it is important to take into account the specificity of the COPs to be tackled to define more efficient data structures. This is crucial especially when the pool of subproblems generated during their resolution is very big which is the case for permutation COPs. Indeed, the complexity of a single-permutation COP of size n is n! which is very high for large problem instances. For example, for a Flow-Shop with 50 jobs to be scheduled on 20 machines, the number of candidate permutations is  $3 \times 10^{64}$  and the number of potential subproblems to be solved is about  $10^{64}$ . In this thesis, we propose a new

data structure called Integer-Vector-Matrix (or IVM) dedicated to permutation COPs. Consequently, we redefine the B&B operators acting on it at execution. Although IVM is less generic than LL it is more efficient in terms of storage and management of the pool of subproblems generated during the resolution of a COP.

- B&B algorithms applied to permutation problems are highly irregular due to the bounding operator [Chakroun 2013c]. Indeed, the explored tree is unpredictable and highly irregular in size and shape from a run to another of the same problem instance. Therefore, work stealing-based work pool parallel model is well-suited for their parallelization as for irregular applications in general [Acar 2013]. In most existing works related to multi-core B&B, the work pool model is implemented using concurrent data structures [Mans 2006, Chakroun 2013a]. In such approach, each thread continuously picks a subproblem from the shared pool and the generated subproblems are returned back to be inserted in the pool. The major problem with this approach is that the use of concurrent data structures is limited in terms of efficiency and scalability. Instead, private data structures are highly recommended [Shavit 2011, Acar 2013]. In this thesis, we revisit the work stealing paradigm on multi-core processors using private IVM and private LL. The challenge here is twofold: (1) Defining the work units and the way they are communicated; (2) Defining victim selection and granularity policies to manage the stealing operations performed on these work units. We first propose an efficient coalesced coding of work units using factoradic-based intervals. Then, we investigate various work stealing strategies based on different victim selection and granularity policies.

- An experimental study performed in [Chakroun 2013b] has shown that the time spent by the B&B evaluating the lower bounds of the generated subproblems is on average between 98% and 99% of its total execution time. This result demonstrates that the bounding operator needs massively parallel computing. On the other hand, coprocessors including GPUs and MIC allow to boost the performance of traditional processors through the combination of a larger number of processing cores, vector-SIMD processing and multi-threading. These specific features raise several issues including the optimization of data transfer between the processor and its coprocessor, vectorization, memory optimization, etc. In this thesis, having in mind these issues, we revisit the parallel bounding model combined with the parallel tree exploration model of B&B algorithms for GPU accelerators and Intel MIC Xeon Phi coprocessors.

This thesis is organized into six chapters. Chapter 2 introduces the factorial number system for permutation problems. This later is used to define our IVM data structure. We first give some examples of permutation COPs: TSP, QAP, Job-Shop and Flow-Shop. Then, we recall the factorial number system and remind to the reader some basic concepts in number systems, such as positional numbering systems and mixed radix systems. Finally, we detail the two main techniques used to convert a permutation into a factorial number, and to transform a factorial number into a permutation.

Chapter 3 describes the conventional serial B&B algorithm, its associated four operators, and the implementation of its pool of subproblems using the LL data structure. Then, the implementation of the pool using our newly proposed IVM data structure is detailed. Finally, some experimental results are reported comparing the performance of the IVM-based B&B to the LL-based B&B in terms of memory and CPU time usages.

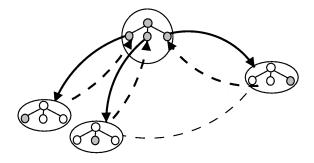

Chapter 4 presents the different parallel models of B&B algorithms and their investigation for different parallel hardware architectures in some related works. Then, B&B is revisited using the IVM data structure and the work stealing paradigm. Five different strategies are presented, experimented and compared considering the IVM and LL data structures.

In Chapter 5, we first present the general design of the coprocessor-accelerated B&B. Then, we describe the implementation of the GPU-accelerated and Phi-accelerated approaches. After that, we report some experimental results comparing the two coprocessor-based many-core implementations and their multi-core implementation counterpart.

Finally, some concluding remarks are drawn in Chapter 6. In addition, we propose some future extensions of the proposed approaches and some perspectives related to the evolution of the context of High Performance Computing and to the generalization of the proposed approaches to other permutation COPs and other B&X tree-based algorithms.

#### CHAPTER 2

# Permutation-based optimization problems

| Contents |                                              |                                       |  |  |  |  |  |

|----------|----------------------------------------------|---------------------------------------|--|--|--|--|--|

| 2.1      | Introduction                                 |                                       |  |  |  |  |  |

| 2.2      | Permutation optimization problems            |                                       |  |  |  |  |  |

|          | 2.2.1                                        | Traveling-salesman problem            |  |  |  |  |  |

|          | 2.2.2                                        | Quadratic assignment problem          |  |  |  |  |  |

|          | 2.2.3                                        | Job-Shop problem                      |  |  |  |  |  |

|          | 2.2.4                                        | Permutation Flow-Shop problem         |  |  |  |  |  |

| 2.3      | Factor                                       | rial number system                    |  |  |  |  |  |

|          | 2.3.1                                        | Definition of number system           |  |  |  |  |  |

|          | 2.3.2                                        | Definition of factorial number system |  |  |  |  |  |

|          | 2.3.3                                        | Operations based on decimal system    |  |  |  |  |  |

|          | 2.3.4 Operations based on factorial system   |                                       |  |  |  |  |  |

| 2.4      | Handling permutations with factorial numbers |                                       |  |  |  |  |  |

|          | 2.4.1                                        | Basic concepts                        |  |  |  |  |  |

|          | 2.4.2                                        | Permutation to factorial number       |  |  |  |  |  |

|          | 2.4.3                                        | Factorial number to permutation       |  |  |  |  |  |

| 2.5      | Concl                                        | usion                                 |  |  |  |  |  |

#### 2.1 Introduction

Many industrial and economic problems are permutation combinatorial optimization problems. Solving these problems consists in finding the optimal permutation of elements among a large finite set of possible permutations. In order to find the optimal permutation, one of the used techniques is to explicitly or implicitly list all the set of possible permutations. The factorial number system is well suited for listing and enumerating these

permutations. This special enumeration system is considered as positional mixed radix system in which the numerical base varies from position to position.

The chapter is divided into three sections. Section 2.2 gives four examples of permutations problems: TSP, QAP, Job-Shop and Flow-Shop. Section 2.3 presents the factorial number system. This section reminds to the reader some basic concepts in number systems, such as positional numbering systems and mixed radix systems. Finally, Section 2.4 details the two main techniques used to convert a permutation into a factorial number, and to transform a factorial number into a permutation.

#### 2.2 Permutation optimization problems

#### 2.2.1 Traveling-salesman problem

In the literature, the traveling salesman problem (TSP) is well studied mostly because of its hardness and the number of its applications [Garey 1979]. The TSP as input gives a set of n cities to travel to. The cost of the trip between each pair of cities is given by a cost matrix. The objective of the problem is to find the tour of all cities that has the lowest cost while visiting each city only once. A more formal description of the problem is generally given in the form of the graph G = (V, A), where  $V = v_1, ..., v_n$  is the set of vertices and  $A = (v_i, v_j)/v_i, v_j \in V$  is the set of edges. Each edge  $(v_i, v_j)$  has an associated cost (or weight)  $c_{ij}$ . Solving this problem requires finding a Hamiltonian circuit for which the total cost of all the arcs is minimal. A number of variants of this problem exist, such as the symmetric TSP (TSTP) where the cost of each vertex follows this property:

$$c_{ij} = c_{ji} \forall i, j \in 1, 2, ..., n$$

(2.1)

When traveling between two cities, the cost of the associated arc is the same no matter the direction, so the graph can be undirected.

The asymmetric TSP (ATSP) on the other hand, takes the form of a complete directed graph where the edges have a different cost (or weight) depending on the direction. The TSP can be represented as a permutation where the order in which each city is visited during the tour is viewed as a sequence which is a permutation of size n. Since this is a tour of all the cities, the last visited city is connected to the first one. Equation 2.2 gives a permutation formulation of the TSP. The cost of a valid tour is the sum of the distances between each pair of adjacent cities in the tour.

$$Minimize \sum_{i=1}^{n-1} C_{\pi(i)\pi(i+1)} + C_{\pi(n)\pi(1)}$$

(2.2)

#### 2.2.2 Quadratic assignment problem

One of the hardest combinatorial optimization problems is the quadratic assignment problem (QAP). Koopmans and Beckmann introduced this problem in 1957 [Koopmans 1957], their objective was to provide a mathematical model for the allocation of indivisible economical activities. The problem consists in finding a location for plants while taking into account the cost of transportation between plants. This makes the QAP more complex than the linear assignment problem (LAP). This particular application of the QAP is called facility location.

Later, Sahni and Gonzalez [Sahni 1976] have proven that the QAP is NP-hard. Two factors have given the QAP the attention of the optimization community: the huge number of real life applications in a variety of domains and its complexity making it well known as one of the fundamental problems in optimization. The QAP is applied in various domains outlined in [Loiola 2007] where the authors propose a review of different applications and mathematical formulations as well as a complete state-of-the-art for heuristic and exact methods applied to the QAP.

The problem originally stated by Koopmans and Beckmann can be described this way: a given set of n plants (or facilities) must be assigned to a set of n locations. The distances between each pair of locations are stored in a distance matrix  $D = (d_{kp})$ , D is a square matrix of size n. The flows between the facilities (for a hospital, this can be the transportations between different clinics) are stored in a matrix  $F = (f_{ij})$ , F is called a flow matrix. The problem is to assign each facility to a location in a way that minimizes the sum of the flows between each pair of facilities. The QAP is more complex than the LAP because not only the cost of each assignment of a facility to a location depends on the distance and the flow between two adjacent facilities, but it also depends on the rest of the assignments of a facility to a location.

Equation 2.3 shows the general mathematical formulation of the QAP, it is called the Koopmans-Beckmann formulation. The term  $d_{kp}$  represents the distance between locations k and p. The term  $f_{ij}$  represents the flow between facilities i and j. The binary variables  $x_{ij}$  represent the assignment of a facility i to a location j. When considering the cost of the act of assigning a facility to a location (e.g. installation cost), the term  $b_{ik}$  represents the cost of the assignment. The sum of the assignment cost for each facility is then added to the overall cost of a solution to QAP. Many researchers omit this term because it is a simple linear assignment that can be optimized easily.

Equation 2.4 shows the uniqueness constraints of QAP (one facility per location, one location per facility).

$$Minimize \sum_{i,j=1}^{n} \sum_{k,p=1}^{n} f_{ij}.d_{kp}.x_{ik}.x_{jp} + \sum_{i,k=1}^{n} b_{ik}.x_{ik} , x \in X$$

(2.3)

$$x \in X \equiv \begin{cases} x \in \{0, 1\} \\ \sum_{i=1}^{n} x_{ij} = 1, j = 1, ..., n \\ \sum_{j=1}^{n} x_{ij} = 1, i = 1, ..., n \end{cases}$$

(2.4)

Later, Lawler [Lawler 1963] proposed a different formulation of the QAP, based on integer linear programming (LP). Lawler's LP formulation replaces the terms  $f_{ij}.d_{kp}$  by a single term  $c_{ijkp}$  representing the cost of assigning a facility i to a location k and assigning a facility j to a location p. These costs are placed in a square matrix of size  $n^2$  called a cost matrix. However, the permutation formulation of the QAP is more pertinent within the context of this thesis. In this case, the QAP can be described as the assignment of n facilities to n adjacent locations, the objective is then to minimize the overall cost of the assignments. It follows that a solution to the QAP can be described as a permutation  $\pi$  of n integers (1, 2, ..., n) which represent the facilities, whereas the positions within the permutation represent the n locations. Equation 2.5 shows this formulation.

$$Minimize \sum_{i,j=1}^{n} f_{ij}.d_{\pi(i)\pi(j)}$$

(2.5)

The use of permutations guarantees that the constraints of the assignment are respected.

As said earlier, Sahni and Gonzalez [Sahni 1976] have proven that the QAP is NP-hard. They argued that it is not even possible to find a polynomial f-approximation algorithm for the QAP.

Different authors have studied the practical complexity of the QAP from various points of view. Roucairol *et al.* [Mautor 1994b] studied how difficult it is for exact methods to solve the QAP. They argued that the structure of the instances is a factor in explaining the difficulty of solving the QAP for exact methods such as Branch-and-Bound. The product of the two matrices can produce many solutions of good quality whose cost is within a very narrow range. Under such conditions, the Branch-and-Bound algorithm can not eliminate many branches in the tree. Many authors use the related notion of flow dominance to explain the hardness of some of the instances. Angel *et al.* [Angel 2002] define flow dominance as: flow dominance is when a few facilities exchange a lot of materials between each other but few materials with the rest of the facilities.

#### 2.2.3 Job-Shop problem

The Job-Shop problem (JSP) is a generalized version of the permutation Flow-Shop problem. Brucker [Brucker 2007] provides a definition of JSP. A set of n jobs  $J_i, J_2, ..., J_n$  must be scheduled on a set of m machines. Every job  $J_i$  is made of  $n_i$  operations defined as  $O_{i,j}$ , i=1,2,...,n and  $j=1,...,n_i$ . There is a precedence constraint which ensures that the sequence of operations  $O_{i,1}, O_{i,2}, ..., O_{i,n_i}$  of every job has to be processed in this specific order on all machines. For operation  $O_{i,j}$  on machine  $M_{i,j}$  with  $j=1,...,n_i$ , we define  $p_{i,j}$  as the processing time of this operation. We assume that each operation  $O_{i,j}$  will be processed on a different machine  $M_{i,j}$ , meaning that  $M_{i,j} \neq M_{i,j+1}$  for  $j=1,...,n_{i-1}$ . The objective of JSP is to find a valid schedule which minimizes the completion time or the makespan  $C_{max}$  of the last operation in the schedule.

The use of multi-permutations makes it possible to have a permutation representation of the JSP [Bierwirth 1996, Ponsich 2010]. Each permutation is a representation of the sequence of operations on one machine. The total number of operations is equal to  $n \times m$ , n being the number of jobs and m being the number of machines. However, Bierwirth points out in [Bierwirth 1996] that due to the different constraints, it is not possible to find a representation of the JSP that uses standard permutations without including invalid solutions in the coding. For example, using a multi-permutation to describe the problem as described earlier, it is possible that two jobs scheduled on two different machines violate the precedence constraint. In order to overcome this obstacle, some authors use weight penalties to progressively discard invalid solutions from the search, or use reparation to transform an invalid solution into a valid one. However, the search can be disrupted if this happens too often. [Bierwirth 1996] provides a new representation for the JSP. This new representation makes use of a single permutation which uses repetition to represent the sequencing of all the operations on all the machines.

The use of this representation means that each solution requires a phase of decoding (or reading) before it is evolved. Using this representation, each job number appears m times within the permutation, i.e. as many times as there are operations that belong to this job. This representation is called an indirect representation. There is no decoding step required when using classic neighborhood and genetic operators, which means that the permutation should be read according to the properties of the problem.

#### 2.2.4 Permutation Flow-Shop problem

In manufacturing environments, it is common to find Permutation Flow-Shop Scheduling Problems [Bonney 1976, King 1980, Allahverdi 1999] where n jobs have to be processed on m machines where the goal is to optimize an objective function. The objective of the

FSP is to schedule a set of n jobs on a set of m machines where each job  $J_1$ ,  $J_2$ , ...,  $J_n$  is processed on the machines  $M_1$ ,  $M_2$ , ...,  $M_m$  organized in the line. Each job  $J_i$  with  $i=1,2,\ldots,n$  is made of a sequence of m operations  $O_{i1}$ ,  $O_{i2}$ , ...,  $O_{im}$  where operation  $O_{ik}$  is the processing of job  $J_i$  on machine  $M_k$  for a processing time  $p_{ik}$  that can not be interrupted. The objective of the FSP is to find a processing order on each machine  $M_k$  which minimizes the time necessary to complete all jobs, also known as the makespan. Within the context of this thesis, each reference to the FSP is actually a reference to the permutation FSP [Allahverdi 1999, Hejazi 2005]. Using Johnson's algorithm [Johnson 1954], it is possible to find an optimal schedule for the FSP in  $O(n \log n)$  steps when m=2. The problem is NP-hard when  $m \geq 3$  [Garey 1976]. This is why it is often tackled using metaheuristics [Basseur 2005] for solving large problem instances.

These are the constraints that a valid FSP solution should satisfy:

- A machine can not start processing a job before the preceding machines have finished processing that job. In other words, machine  $M_j$  can not process operation  $O_{ij}$  before it is completed on machine  $M_{j-1}$ .

- An operation can not be interrupted, and since a machine processes one job at a time, the machines are critical resources.

- The sequence of jobs must be the same on all machines, e.g. if job  $j_3$  is processed in second position on the first machine, job  $j_3$  must also be processed in second position on all the other machines.

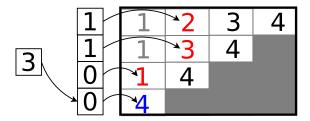

Figure 2.1 shows an example of an FSP instance where n=3 and m=4, it also shows the optimal solution.

#### 2.3 Factorial number system

The proposed IVM data structure (presented in Chapter 3) and the coding of work units in the multi-core context (presented in Chapter 4) are based on the factorial number system. The definition of this system is quite different compared to other known systems such as decimal and binary systems. Subsection 2.3.1 reminds the main concepts used to define any number system. Subsection 2.3.2 presents the factorial number system. Then, Subsection 2.3.3 and Subsection 2.3.4 explain the implementation of some arithmetic operations in the factorial system. The four arithmetic operations used in our work are addition, subtraction, division, and comparison. These factoradic-based operators are used in Chapter 4 for the factoradic interval-based work stealing strategies.

Figure 2.1: Illustration of a permutation FSP where n=3 and m=4. The table shows the processing times of the jobs on each machine. The Gantt diagram shows the optimal solution for this particular instance.

- **Comparison:** This operation is relatively easy to implement. It consists of comparing all the positions of the two operands starting with the most significant position (i.e. from left to right).

- **Addition:** This operation is directly implemented in the factorial system. Subsection 2.3.4 explains the method used to perform this operation.

- **Subtraction:** The algorithm of this operation is similar to the one used for the addition. Subsection 2.3.4 also explains the implementation of this operation.

- Division: Unlike addition and subtraction, the division is more difficult to implement

for factorial numbers. In our work, division is implemented by converting factorial

numbers to decimal numbers, thereafter, by performing division of these decimal

numbers, and finally, by converting the result of the division to a factorial number.

Subsection 2.3.3 explains the implementation of division using decimal system.

#### 2.3.1 Definition of number system

A number system, called also numeral system or system of numeration, is a writing system or a mathematical notation in order to express and represent a set of numbers using symbols in a consistent manner. A number system is defined by its digits, its bases, also called radixes, and its place-values. This subsection reminds these concepts before their definitions for the factorial system are given in Subsection 2.3.2.

#### Digits:

Etymologically, the word *digit* comes from ancient Latin word *digit* which means fingers. Therefore, this word is related to the decimal system where ten digits are used like the ten fingers. However, the word digit is used nowadays for all other number systems including the binary system where the word bit is more appropriate. A number is a sequence of digits which can have an arbitrary length. Each digit, in a number system, represents an integer. In the decimal and the hexadecimal systems, for instance, the digits 1 and *A* represent the integers one and ten, respectively. In Roman numerals, where seven symbols are used, each symbol represents also a different integer as shown in Table 2.1.

| Symbol | Value |

|--------|-------|

| I      | 1     |

| V      | 5     |

| X      | 10    |

| L      | 50    |

| С      | 100   |

| D      | 500   |

| M      | 1,000 |

Table 2.1: Roman digits and their values.

There is a particular number system defined only with one digit. This simplest numeral system is called the unary numeral system, and can be used to represent all natural numbers. In order to represent any number N, an arbitrarily symbol, which represents the integer 1, is simply repeated N times. This system is often used in tallying. For example, using the tally mark |, the number 5 is represented as | | | | | | Unlike multiplication or division, the other operations, namely addition, subtraction and comparison, are particularly simple to be implemented in the unary system. Compared to other numeral systems, the unary system is not used in practice for large calculations but can be convenient for small operations, like representing a number with fingers. Unary system is used in some data compression algorithms such as Golomb coding [Golomb 1966].

#### Place-value:

Roman system, used in ancient Rome, employs combinations of letters from the Latin alphabet in order to express numbers. For example, the first ten numbers can be expressed as follows: I, II, III, IV, V, VI, VII, VIII, IX, X. In this system, numbers are written by combining symbols and adding or subtracting the values this symbols. For example, XIII means

thirteen by adding a ten and three ones, and IX means nine by subtracting one from ten. Unlike the decimal system, there is no zero in Roman system and symbols do not represent tens or hundreds according to their positions. Therefore, unlike Roman system, which is not a positional system, decimal system is a positional numeral system.

Ancient number systems, like Roman system, were not positional, and all of the number systems most commonly used today, like binary system, are positional systems. Place-value is a positional system of notation in which the position of a number determines its value. In other words, the value of a number in such system is determined not just by the digits but also by the positions of each of the digits. For example, all place-values, also called order of magnitudes, in the unary system are equal to 1, the places-values of decimal are powers of ten, like ones-place, tens-places, hundreds-place, etc. One of the advantages of positional notation is the use of the same symbols for different order of magnitudes. This greatly simplifies arithmetic operations.

#### Radix:

Etymologically, the word radix is a Latin word for the word root, and root is a synonym for base in the arithmetical sense. In a positional numeral system, the radix is the number of unique digits, including zero, used to represent numbers. For example, the radix is ten for decimal system since this system uses ten digits from 0 through 9 in order to represent its numbers. In a positional numeral system, the number X and the radix Y are conventionally written as  $(X)_Y$ . However, the radix can be implicitly assumed and not written for some systems like decimal or unary systems.

Mixed radix numeral systems are non-standard positional numeral systems. Unlike most common systems, where the base is similar to all positions, the numerical base can vary from position to position. Such representation is used when a value or a number is written using a sequence of units that are each a multiple of the next smaller unit. For example, this type of number systems can be found when expressing time. A time of 10 hours, 30 minutes, and 50 seconds might be expressed as 10:30:50 in mixed-radix notation where the radix of the first and second positions is 60 and the radix of the third position is 24.

In positional fixed radix number system, where the base R is fixed, each digit  $a_i$  in any number  $(a_{n-1}...a_0)_R$  is an integer in the range 0 to (R-1) and the number is interpreted as shown in Equation (2.6).

$$(a_{n-1}...a_0)_R = a_{n-1}R^{n-1} + ... + a_1R^1 + a_0R^0$$

(2.6)

Since Equation (2.6) is a polynomial in R, fixed radix system can be also called polynomial system. The decimal and binary systems are both fixed-radix systems, with a radix of 10 and 2, respectively. Fractional values can also be represented with the same polynomial notation.

$$0.a_1a_2...a_n = a_{-1}R^{-1} + a_2R^{-2} + ... + a_nR^{-n}$$

(2.7)

In mixed-base or radix number system, the digit  $a_i$  in any number belongs to the interval 0 to  $R_i$ , where  $R_i$  is not the same for all the values of i. The number is then interpreted as shown in Equation (2.8).

$$a_{n-1}...a_0 = (...((a_{n-1} R_{n-1}) + a_{n-2})R_{n-2} + ... + a_1)R_0 + a_0$$

(2.8)

For example, 10 hours 30 minutes 50 seconds is interpreted as

$$10:30:50 = ((10 \times 24 + 30) \times 60 + 50 \ seconds \tag{2.9}$$

#### 2.3.2 Definition of factorial number system

Factorial system, also called factoradic, is a mixed radix number system which is well adapted for numbering permutations. This system is not named like most numeral systems. For example, unary, binary and decimal are named like this because their radixes are one, two and ten, respectively. Unlike these systems, the factorial system is named according to its place-value instead of its mixed-radix. The term "factorial number system" is used the first time recently in 1998 [Knuth 1998] while the French name *numération factorielle* is first used in 1888 [Laisant 1888]. The term "factoradic" appears to be much more recent [McCaffrey 2003]. General properties of mixed radix number systems also apply to the factorial system.

As explained in Table 2.2, the  $i^{th}$  digit from the right has base i and the place-value i!. Therefore, the  $i^{th}$  digit must be less than i. And in order to compute the value of a number, the value of the  $i^{th}$  digit must be multiplied by i!. From this, it follows that the rightmost digit is always 0, the second can be 0 or 1, the third 0, 1 or 2, and so on.

| Place          | ••• | 7 <sup>th</sup> | $6^{ m th}$ | $5^{ m th}$ | $4^{ m th}$ | $3^{\mathrm{rd}}$ | $2^{\mathrm{nd}}$ | $1^{\mathrm{st}}$ |

|----------------|-----|-----------------|-------------|-------------|-------------|-------------------|-------------------|-------------------|

| Radix/base     |     | 7               | 6           | 5           | 4           | 3                 | 2                 | 1                 |

|                |     | 6!              | 5!          | 4!          | 3!          | 2!                | 1!                | 0!                |

| Place-value    | ••• | =               | =           | =           | =           | =                 | =                 | =                 |

|                |     | 720             | 120         | 24          | 6           | 2                 | 1                 | 1                 |

|                |     | 0               | 0           | 0           | 0           | 0                 | 0                 | 0                 |

|                |     | 1               | 1           | 1           | 1           | 1                 | 1                 |                   |

|                |     | 2               | 2           | 2           | 2           | 2                 |                   |                   |

| allowed digits | ••• | 3               | 3           | 3           | 3           |                   |                   |                   |

|                |     | 4               | 4           | 4           |             |                   |                   |                   |

|                |     | 5               | 5           |             |             |                   |                   |                   |

|                |     | 6               |             |             |             |                   |                   |                   |

Table 2.2: Factorial system and its radixes, place-values and digits for the seven first positions.

It is possible to define factorial numbers without writing the rightmost digit since it is always equal to zero. In our thesis report, a factorial number representation will be flagged by a subscript "!", so for instance  $(322110)_!$  stands for  $(3_{5!}2_{4!}2_{3!}1_{2!}1_{1!}0_{0!})$ . In principle, the factorial system may be extended to represent fractional numbers. However, the natural extension of place-values (-1)!, (-2)!, etc. are undefined. In factorial system, the symmetric choice of radix values n = 0, 1, 2, 3, 4, etc. after the point may be used instead. The correspondent place-values are therefore 1/(0!), 1/(1!), ..., 1/(n!), etc. In our work, factorial fractional numbers are not used.

#### 2.3.3 Operations based on decimal system

This subsection explains the used methods, in our work, to perform the division operation in the factorial system. Unlike other operations, the division is hardly feasible directly in the factorial system. Another way to do this operation is to convert the dividend and the divisor to the decimal system, to perform the division in the decimal system, and thereafter to convert the result to the factorial system. So this subsection explains how to convert a factorial number to a decimal number, and how to convert a decimal number to a factorial number.

#### Decimal to factoradic:

When converting a decimal number into its factorial representation, digits are produced from right to left. This conversion consists in repeatedly dividing the number by the radixes 1, 2, 3, etc. After each division, the remainder should be considered as the digit. The division operation continues with the integer quotient until this quotient becomes 0. Let assume a decimal number D=349 to convert into a factorial number. This conversion is done using successive Euclidean division as shown in Equation (2.10).

$$349 = 1 \times 349 + 0$$

$$349 = 2 \times 174 + 1$$

$$174 = 3 \times 58 + 0$$

$$58 = 4 \times 14 + 2$$

$$14 = 5 \times 2 + 4$$

$$2 = 6 \times 0 + 2$$

$$(2.10)$$

Euclidean division is the operation of division of two integers, which produces a quotient and a remainder. Each line of Equation (2.10) represents an Euclidean division  $Q_i = i \times Q_{i+1} + R_i$  such as:

- $Q_{i+1}$  is the quotient of the division  $\frac{Q_i}{i}$

- $R_i$  is the reminder of this division

- $Q_1 = A$  is the decimal number to convert

- $Q_{n+1}$  is always equal to zero and is the last quotient

- $R_1$  is always equal to zero and is the first remainder

The factorial representation F of A is equal to concatenation of all reminders, as shown in Equation (2.11), is  $F = (R_n ... R_2 R_1)_! = 242010$ .

$$349 = 1 \times 349 + 0$$

$$= 1 \times (2 \times 174 + 1) + 0$$

$$= 1 \times (2 \times (3 \times 58 + 0) + 1) + 0$$

$$= 1 \times (2 \times (3 \times (4 \times 14 + 2) + 0) + 1) + 0$$

$$= 1 \times (2 \times (3 \times (4 \times 5 \times 2 + 4) + 2) + 0) + 1) + 0$$

$$= 1 \times (2 \times (3 \times (4 \times 5 \times 2 + 4) + 2) + 0) + 1) + 0$$

$$= 1 \times (2 \times (3 \times (4 \times 5 \times 6 \times 0 + 2) + 4) + 2) + 0) + 1) + 0$$

$$= 25! + 44! + 23! + 02! + 11! + 00!$$

$$= (242010)!$$

(2.11)

Algorithm 1 explains the used method to perform this conversion.

#### **Algorithm 1** DECIMAL-TO-FACTORIAL(D)

- 1: Place  $\leftarrow 1$

- 2: while  $D \neq 0$  do

- 3:  $F_{i-1} \leftarrow D \mod i$

- 4:  $D \leftarrow D \operatorname{\mathbf{div}} i$

- $5: \qquad i \leftarrow i\!+\!1$

- 6: end while

- 7: return F

#### Factoradic to decimal:

Converting a factorial number to a decimal number is simpler. Let  $(R_{n-1}...R_1R_0)_!$  a factorial number. In order to have its decimal equivalent, it suffices to calculate the value of the polynomial  $\sum_{i=0}^{i=n-1} R_i$  i!. The conversion of a factorial number to its decimal equivalent is therefore a sum of multiplications, while the conversion of a decimal number to its factorial equivalent is a concatenation of divisions. Algorithm 2 explains this sum of multiplications.

#### **Algorithm 2** FACTORIAL-TO-DECIMAL(F)

- 1: Place-value  $\leftarrow 1$

- 2:  $D \leftarrow 0$

- 3: **for**  $i \leftarrow 1$  **to** n **do**

- 4: Place-value  $\leftarrow$  Place-value  $\times$  i

- 5:  $D \leftarrow D + F_i \times Place-value$

- 6: end for

- 7: return D

#### 2.3.4 Operations based on factorial system

It is possible to use the conversion to the decimal system for implementing the addition and subtraction. However, this results in loss of performance. The other technique is to directly implement these operations into the factorial system. This subsection first explains the implementation of the addition and then the implementation of the subtraction.

#### Addition:

Let assume two factorial numbers  $A=(A_{n-1}...A_1A_0)_!$  and  $B=(B_{n-1}...B_1B_0)_!$  to be added and both having the size n. As these numbers are factorial, both conditions  $\forall i,A_i\leq i$  and  $\forall i,B_i\leq i$  are always true. The addition of A and B would be simple if  $\forall i,A_i+B_i\leq i$ . In this case, the result of the addition would be  $C=(C_{n-1}...C_1C_0)_!$  such as  $\forall i,C_i=A_i+B_i$ . However, the condition  $\forall i,A_i+B_i\leq i$  is not always satisfied. Let assume i such as  $A_i+B_i>i$ . The value of  $C_i$  can be calculated as explained in Equation (2.12).

$$C_{i} = A_{i} i! + B_{i} i!$$

$$= [A_{i} + B_{i}]i!$$

$$= [(i+1) - (i+1) + (A_{i} + B_{i})]i!$$

$$= (i+1)i! + [-(i+1) + (A_{i} + B_{i})]i!$$

$$= (i+1)! + [(A_{i} + B_{i}) - (i+1)]i!$$

(2.12)

Therefore, there is a carry +1 for the calculation of  $C_{i+1}$ , and  $C_i = (A_i + B_i) - (i+1)$  since the rule of Equation (2.13) is always true.

$$[(A_i \le i) \text{ and } (B_i \le i) \text{ and } (A_i + B_i > i)] \Rightarrow 0 \le [(A_i + B_i) - (i+1)] \le i$$

(2.13)

Equation (2.14) gives the value of  $C_i$  for any values of  $A_i$  and  $B_i$ .

$$C_{i} = \begin{cases} (A_{i} + B_{i}) & If (A_{i} + B_{i}) \leq i \\ (A_{i} + B_{i}) - (i+1) & Otherwise \end{cases}$$

(2.14)

Algorithm 3 explains the method used for the addition of A and B. The algorithm proceeds from the least significant position to the most significant one, in other words, from right to left. So, it is possible to check whether there is a carry +1 when computing  $C_i$ . If this is the case, this carry is taken into account when computing  $C_{i+1}$ .

#### Algorithm 3 FACTORIAL-ADDITION(A, B)

```

1: for i \leftarrow 0 to (n-1) do

2: C_i \leftarrow C_i + A_i + B_i

3: if C_i > i then

4: C_i \leftarrow A_i - (i+1)

5: C_i + 1 \leftarrow 1

6: end if

7: end for

8: return C

```

#### **Subtraction:**

Let assume two factorial numbers  $A = (A_{n-1}...A_1A_0)!$  and  $B = (B_{n-1}...B_1B_0)!$ . As these numbers are factorial, both conditions  $\forall i, A_i \leq i$  and  $\forall i, B_i \leq i$  are always satisfied. The objective of this subsection is to explain how to perform a subtraction A - B when assuming  $A \geq B$ . To facilitate the explanation, both numbers are assumed to have the same size n. If the size of B is smaller than A, then it is possible to complete B with zeros at the left.

The subtraction A-B would be simple if  $\forall i, A_i \geq B_i$ . In this case, the result of the subtraction would be  $C=(C_{n-1}...C_1C_0)_!$  such as  $\forall i, C_i=A_i-B_i$ . However, the condition  $\forall i, A_i \geq B_i$  is not always satisfied. Let assume i such as  $A_i < B_i$ . The value of  $C_i$  can be computed as explained in Equation (2.15).

$$C_{i} = A_{i} i! - B_{i} i!$$

$$= [A_{i} - B_{i}]i!$$

$$= [-(i+1) + (i+1) + (A_{i} - B_{i})]i!$$

$$= [-(i+1)]i! + [(i+1) + (A_{i} - B_{i})]i!$$

$$= [-1](i+1)! + [(i+1) + (A_{i} - B_{i})]i!$$

(2.15)

Therefore, there is a carry -1 to be taken into account when computing  $C_{i+1}$ , and  $C_i = (A_i + B_i) - (i+1)$  since the rule of Equation (2.16) is always true.

$$[(A_i \le i) \ and \ (B_i \le i) \ and \ (A_i < B_i)] \Rightarrow 0 \le [(A_i - B_i) + (i+1)] \le i$$

(2.16)

Equation (2.17) gives the value  $C_i$  for any values of  $A_i$  and  $B_i$ .

$$C_i = \begin{cases} (A_i - B_i) & If (A_i - B_i \ge 0) \\ (A_i - B_i) + (i+1) & Otherwise \end{cases}$$

(2.17)

Algorithm 4 explains the operation of the subtraction A - B. Like the addition, the subtraction algorithm proceeds from the least significant position to the most significant position. It is possible to check if there is a carry -1 when computing  $C_i$ . If this is the case, this carry is taken into account when computing  $C_{i+1}$ .

## Algorithm 4 FACTORIAL-SUBTRACTION (A, B)

```

1: for i \leftarrow 0 to (n-1) do

```

2:

$$C_i \leftarrow C_i + A_i - B_i$$

3: if

$$C_i < 0$$

then

4:

$$C_i \leftarrow C_i + (i+1)$$

5:

$$C_{i+1} \leftarrow -1$$

- 6: end if

- 7: end for

- 8: return C

# 2.4 Handling permutations with factorial numbers

## 2.4.1 Basic concepts

## Representation of a permutation:

In the remainder of this section, three representations are used to describe a permutation  $\pi$ .

• The element-based representation:  $\pi = \pi_0 \pi_1 ... \pi_{n-1}$ . The positions are implicitly assumed sorted. The presentation gives therefore the position of each element. For example, the element 7 of Equation (2.18) is scheduled at the position 2.

$$\pi = 527038614 \tag{2.18}$$

• The set-based representation:  $\pi = \{(0, \pi_0), (1, \pi_1), ..., (n-1, \pi_{n-1})\}$ . In this representation, the permutation is described as a set of pairs. For each pair, the first part gives the position, and the second part gives the element of this position. The example of Equation (2.18) can be written by Equation (2.19).

$$\pi = \{(0,5), (1,2), (2,7), (3,0), (4,3), (5,8), (6,6), (7,1), (8,4)\}$$

(2.19)

• The position-based representation: It is possible to represent a permutation by assuming that the elements are implicitly sorted. Therefore, it is necessary to give the position of each element. The examples of Equation (2.18) and (2.19) can be written using Equation (2.20).

$$\pi = 371480625 \tag{2.20}$$

To facilitate the understanding of the methods of this section, it is therefore important to see a permutation as a bijective relationship between the components of a vector of elements and the components of a vector of positions.

#### **Inversions:**

Lehmer code (explained in this chapter) and inversion table (explained in Appendix B) are both based on the inversion concept. Let assume  $\pi$  a permutation. An inversion in a permutation  $\pi = \pi_0 \pi_1 ... \pi_{(n-1)}$  is a pair  $(\pi_i, \pi_j)$  which satisfies the two conditions stated in Equation (2.21).

$$(\pi_i, \pi_j)$$

is an inversion  $\iff$   $(i < j)$  and  $(\pi_i > \pi_j)$  (2.21)

In this section,

•  $Inversions(\pi)$  indicates all the inversions of a permutation  $\pi$ ;

$$Inversions(\pi) = \{(\pi_i, \pi_j)/(i < j) \text{ and } (\pi_i > \pi_j)\}$$

(2.22)

•  $Inversions(\pi_i, \pi)$  indicates all the inversions of a permutation  $\pi$  where  $\pi_i$  appears at the left side of the pairs;

$$Inversions(\pi_k, \pi) = \{(\pi_i, \pi_i) \in Inversions(\pi)/i = k\}$$

(2.23)

•  $Inversions(\pi, \pi_i)$  indicates all the inversions of a permutation  $\pi$  where  $\pi_i$  appears at the right part of the pairs;

$$Inversions(\pi, \pi_k) = \{(\pi_i, \pi_j) \in Inversions(\pi)/j = k\}$$

(2.24)

If all elements of a permutation are ordered, then this permutation contains no inversions. A permutation with no inversions is called identity permutation. Equation (2.25) gives some examples to illustrate all these concepts.

$$Inversions(527038614) = \{(5,2), (5,0), (5,3), (5,1), (5,4), (2,0), (2,1), ..., (6,4)\}$$

$$Inversions(5,527038614) = \{(5,2), (5,0), (5,3), (5,1), (5,4)\}$$

$$Inversions(527038614,0) = \{(5,0), (2,0), (7,0)\}$$

$$Inversions(012345678) = \emptyset$$

$$(2.25)$$

## **Basic vector operations:**

In the explanation of the two methods of the conversion between factorial numbers and permutations, three basic operations for handling vectors are used.

- The first operation, called Vector-INITIALIZE-ZERO accepts as input a vector, and initializes each position of the vector by zero. This operation is used in Subsection 2.4.2

- The second operation, called VECTOR-INITIALIZE accepts as input a vector, initializes each position of this vector by a number equal to its position, and returns the initialized vector. This operation is used in Subsection 2.4.3

- The third operation, called VECTOR-SELECT, receives as input a vector v and a position i, reads the integer r located at position i of vector v (i.e.  $r=v_i$ ), shifts all the elements located at the right of i with one position towards the left, and returns the integer r. This operation is used in Subsection 2.4.3

#### Algorithm 5 Vector and some of its basic operations

```

1: procedure VECTOR-INITIALIZE-ZERO(V)

for i \leftarrow 0 to (N-1) do

2:

V_i \leftarrow 0

3:

end for

4:

5: end procedure

6:

7: procedure VECTOR-INITIALIZE(V)

8:

for i \leftarrow 0 to (N-1) do

V_i \leftarrow i

9:

end for

10:

11: end procedure

12:

13: procedure VECTOR-SELECT(V,I)

14:

\mathbf{r} \leftarrow V_I

for i \leftarrow I to (N-1) do

15:

V_i \leftarrow V_{i+1}

16:

17:

end for

return r

18.

19: end procedure

```

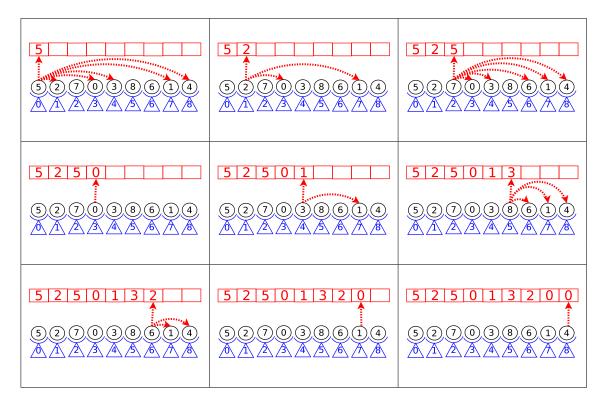

#### 2.4.2 Permutation to factorial number