# Contributions to the Rigorous Design of Concurrent Component-Based Software and Systems Using BIP

Simon Bliudze

#### ▶ To cite this version:

Simon Bliudze. Contributions to the Rigorous Design of Concurrent Component-Based Software and Systems Using BIP. Computer Science [cs]. Université de Lille, 2024. tel-04567479

## HAL Id: tel-04567479 https://hal.univ-lille.fr/tel-04567479

Submitted on 3 May 2024

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Habilitation à Diriger des Recherches Université de Lille

École Graduée MADIS-631 Spécialité : Informatique

## Simon Bliudze

Université de Lille, CRIStAL & Centre Inria de l'Université de Lille Équipe-Projet SPIRALS

# Contributions to the Rigorous Design of Concurrent Component-Based Software and Systems Using BIP

Soutenue le 08 mars 2024 devant le jury composé de

Rapporteurs:

Susanne Graf - DR CNRS au Verimag

Christian Perez - DR Inria au Centre Inria de Lyon

Gianluigi Zavattaro - Professeur à University of Bologna, Italie

Examinateurs:

Panagiotis Katsaros - Professeur à Aristotle University of Thessaloniki, Grèce

Olga KOUCHNARENKO - Professeure à l'Université de Franche-Comté

Garante:

Laurence Duchien - Professeure à l'Université de Lille

#### Abstract

The work presented in the manuscript was carried out in the framework of the Rigorous System Design (RSD) approach. This approach emphasizes multiple levels of separation of concerns. It enforces behavioural properties through semantics-preserving transformations. The RSD flow involves designing an application model, verifying elementary properties, extending the model with platform components, and generating executable code. The approach is applied to various domains, including embedded systems, cyber-physical systems, autonomous systems, and digital twins. The three main chapters summarise the key contributions of the author.

Chapter 2 explores the classical semantics of BIP, a robust component framework central to the RSD methodology. It introduces the theory of architectures, a key element enabling the combination of predefined BIP design patterns to enforce desired behavioural properties. The design process, starting from system requirements and leading to the C++ implementation, is illustrated using the CubETH nano-satellite on-board software case study.

Chapter 3 develops a formal algebraic framework for comparing the expressive power of component-based frameworks. It applies this framework to analyse the expressiveness of the BIP framework. Additionally, an alternative "offer" semantics of BIP is introduced, exploring its relationship with the classical semantics.

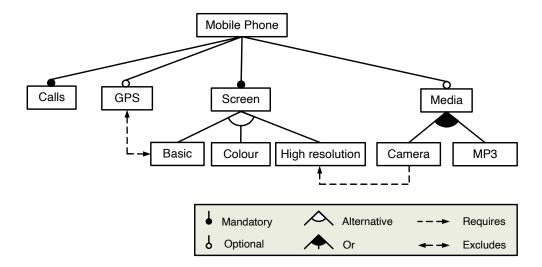

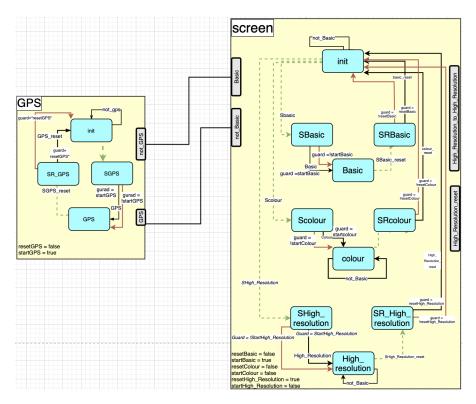

Chapter 4 addresses the adaptation of the RSD approach to general-purpose software development. It introduces JavaBIP, a Java implementation of BIP-inspired coordination mechanisms. JavaBIP utilizes Java annotations and reflection mechanisms to define BIP models associated with Java objects. The chapter details the coordination mechanisms, modular architecture, and the dynamic addition/removal of components in JavaBIP. Two ongoing applications in Cloud Computing and Software Variability, leveraging JavaBIP, are highlighted.

Future work directions are outlined, including the need for a unifying modelling framework for self-adaptive systems, exploration of architecture styles, development of model extraction mechanisms to address software evolution, ensuring model-software adequation through runtime monitoring and dynamic approaches, and addressing the challenge of distributed implementation for scalability while maintaining expressiveness in coordination mechanisms.

#### Résumé

Le travail présenté dans le manuscrit a été réalisé dans le cadre de l'approche de Conception Rigoureuse des Systèmes (RSD). Cette approche met l'accent sur plusieurs niveaux de séparation des préoccupations et impose des propriétés comportementales grâce à des transformations préservant la sémantique. Le flux RSD implique la conception d'un modèle d'application, la vérification des propriétés élémentaires, l'extension du modèle avec des composants de plateforme, et la génération de code exécutable. L'approche est appliquée à divers domaines, notamment les systèmes embarqués, les systèmes cyber-physiques, les systèmes autonomes et les jumeaux numériques. Les trois principaux chapitres résument les principales contributions de l'auteur.

Le chapitre 2 explore la sémantique classique de BIP, un cadre de composants robuste au cœur de la méthodologie RSD. Il introduit la théorie des architectures, un élément clé permettant la combinaison de motifs de conception BIP prédéfinis pour imposer des propriétés comportementales souhaitées. Le processus de conception, partant des exigences du système et aboutissant à l'implémentation C++, est illustré à l'aide de l'étude de cas du logiciel embarqué du nano-satellite CubETH.

Le chapitre 3 développe un cadre algébrique formel pour comparer la puissance expressive des cadres basés sur les composants. Il applique ce cadre pour analyser l'expressivité du cadre BIP. De plus, une sémantique alternative "offre" de BIP est introduite, explorant sa relation avec la sémantique classique.

Le chapitre 4 aborde l'adaptation de l'approche RSD au génie logiciel généraliste. Il introduit JavaBIP, une implémentation Java de mécanismes de coordination inspirés de BIP. JavaBIP utilise des annotations Java et des mécanismes de réflexion pour définir des modèles BIP associés à des objets Java. Le chapitre détaille les mécanismes de coordination, l'architecture modulaire, et l'ajout/suppression dynamique de composants dans JavaBIP. Deux applications en cours de développement dans les domaines du Cloud Computing et de la Variabilité logicielle, exploitant JavaBIP, sont mises en avant.

Les orientations futures sont évoquées, notamment la nécessité d'un cadre de modélisation unificateur pour les systèmes auto-adaptatifs, l'exploration des styles d'architecture, le développement de mécanismes d'extraction de modèles pour traiter l'évolution des logiciels, l'assurance de l'adéquation modèle-logiciel par le biais de la surveillance en temps réel et des approches d'analyse dynamique, ainsi que le défi d'une implémentation distribuée permettant le passage à l'échelle tout en maintenant l'expressivité des mécanismes de coordination.

#### Acknowledgments

I am very grateful to the members of my HDR jury for accepting to serve on the committee and for the stimulating questions and comments during the defence. Particularly, I would like to thank Susanne Graf, Christian Perez and Gianluigi Zavattaro for their time and patience when reviewing the thesis.

Many thanks are due to the examiners and colleagues, Panagiotis Katsaros and Olga Kouchnarenko. A significant part of Chapter 2 presents the results obtained within the ESA-funded project "Catalogue of System and Software Properties" prepared and lead by Panagiotis, which set up the framework for numerous opportunities for fruitful interactions and, in-between, the pleasant time spent, particularly, in Thessaloniki. Even though the results of our recent collaboration with Olga did not make it into the manuscript, I would like to thank her for her comments on the draft versions of parts of the manuscript. Separate thanks are due to Olga for presiding over the defence.

I am deeply grateful to my advisor, Laurence Duchien, for her gentle but resolute guidance. Having the patience to wait out while I was taking my time to work on the manuscript, Laurence offered that invaluable kind of advice that always comes at the right moment and is so much on the spot *once received* that one is almost ashamed of having had to ask.

Many thanks to Lionel Seinturier, the entire SPIRALS team and the colleagues from the Inria Centre at the University of Lille and from CRIStAL for having created and maintained the friendly working environment that was indispensable for the work on the manuscript.

A separate thank you to Hélène Touzet for her support and the final nudge to push me over the crest when my motivation was flailing.

No thanks would be enough to express my gratitude to my long-time mentor, Joseph Sifakis. Most of the work presented in Chapter 2 has been carried out under his guidance. The expressiveness study (Chapter 3) and the JavaBIP project (Chapter 4) were heavily inspired by his thinking.

Of course, this work would not have been possible without the precious collaborations with my co-authors and students. Mentioning all of them here would be impossible but I would particularly like to thank Panagiotis Katsaros, Paul Attie, Mohammad Jaber and my former PhD students Anastasia Mavridou, Eduard Baranov, Alina Zolotukhina, Trình Lê Khánh and Salman Farhat.

Last but not least, I would not be writing these lines, neither the manuscript, nor the papers that underly it, if it were not for the love and unflailing support from Katia, Tom and my parents to whom I am deeply and forever gratefully in debt.

# Contents

| Li | st of            | f Figures                              | ix |

|----|------------------|----------------------------------------|----|

| Li | $\mathbf{st}$ of | f Tables                               | xi |

| 1  | Inti             | roduction                              | 1  |

|    | 1.1              | The Rigorous System Design approach    | 1  |

|    | 1.2              | Structure of the manuscript            | 3  |

| 2  | BIF              | P-based Rigorous System Design flow    | 5  |

|    | 2.1              | The BIP component framework            | 5  |

|    | 2.2              | Architectures: Design patterns for BIP | 11 |

|    | 2.3              | From specifications to a system model  | 19 |

|    | 2.4              | Key contributions                      | 26 |

| 3  | A fe             | Formal study of expressiveness         | 29 |

|    | 3.1              | Algebraic formalisation                | 29 |

|    | 3.2              | Expressiveness of BIP                  | 36 |

|    | 3.3              | The offer predicate                    | 42 |

|    | 3.4              | Key contributions                      | 46 |

| 4  | Jav              | $_{ m raBIP}$                          | 47 |

|    | 4.1              | Quick tour of JavaBIP                  | 47 |

|    | 4.2              | Implementation                         | 54 |

|    | 4.3              | Dynamicity                             | 59 |

|    | 4.4              | Applications                           | 59 |

|    | 4.5              | Key contributions                      | 65 |

| 5  | Cor              | nclusion and future work               | 67 |

| Bi | bliog            | graphy                                 | 71 |

# List of Figures

| A simplified example of the RSD flow instantiation                                              | 2                                                     |

|-------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| Components and behaviour for Examples 2.1.5 and 2.1.6                                           | 7                                                     |

|                                                                                                 | 9                                                     |

| Relation between ports of an architecture and of its operand components                         | 13                                                    |

| The BIP specification of the Failure Monitor architecture                                       | 14                                                    |

| Components and architecture for the Mutual Exclusion architecture example                       | 16                                                    |

| Compound behaviour $\sigma(A_{12}(C_1, C_2))$                                                   | 17                                                    |

| Projections of reachable states of the compound behaviours onto $\sigma(A_{id}(C_1, C_2, C_3))$ | 18                                                    |

| High-level illustration of the CSSP design process                                              | 20                                                    |

| 1                                                                                               | 21                                                    |

|                                                                                                 | 23                                                    |

| Behavior refinement to ensure the validity of architecture assumptions                          | 25                                                    |

|                                                                                                 | 20                                                    |

|                                                                                                 |                                                       |

|                                                                                                 | 41                                                    |

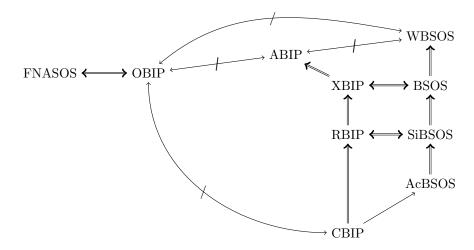

| Expressiveness relations among all the considered frameworks                                    | 45                                                    |

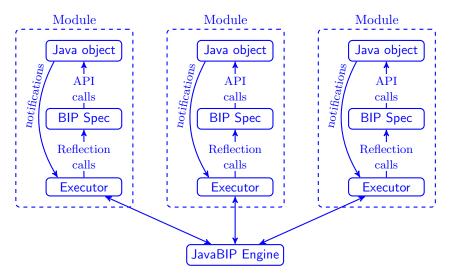

| High-level view of the JavaBIP runnable system architecture                                     | 48                                                    |

|                                                                                                 |                                                       |

|                                                                                                 |                                                       |

| - · · · · · · · · · · · · · · · · · · ·                                                         |                                                       |

|                                                                                                 | 52                                                    |

|                                                                                                 | 53                                                    |

| JavaBIP software architecture.                                                                  | 54                                                    |

| JavaBIP models of one tracker and two peers                                                     | 57                                                    |

| Performance diagrams                                                                            | 58                                                    |

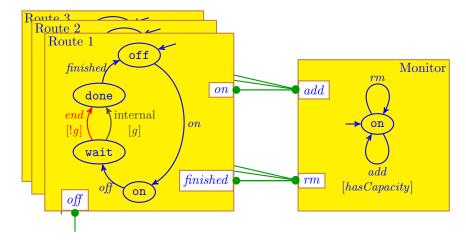

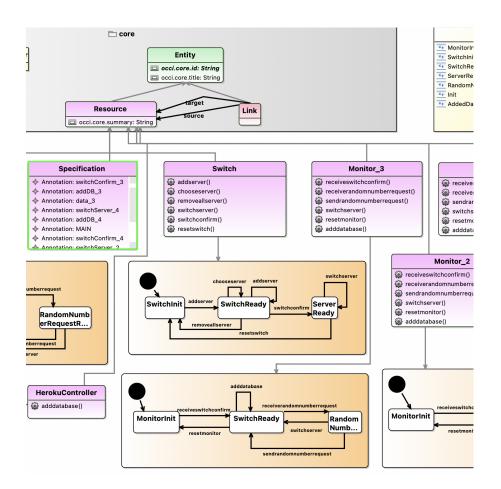

| Fragment of the OCCIware design of Monitor-Switch Web application                               | 62                                                    |

|                                                                                                 | 62                                                    |

| •                                                                                               | 63                                                    |

| Fragment of the generated JavaBIP specification                                                 | 64                                                    |

|                                                                                                 | Components and behaviour for Examples 2.1.5 and 2.1.6 |

# List of Tables

| 2.1 | Algebraic representations of the connectors in Figure 2.2                           | 10 |

|-----|-------------------------------------------------------------------------------------|----|

| 2.2 | Interfaces of the coordinating components of the Failure Monitor architecture       | 14 |

| 2.3 | Preparation and maintenance responsibilities associated with the CSSP process roles | 23 |

| 2.4 | Design-time responsibilities associated to the CSSP process roles                   | 24 |

|     | Expressiveness comparison relations                                                 |    |

| 4.1 | Engine times and BDD Manager peak memory usages                                     | 58 |

# Introduction

Modern software systems are inherently concurrent. They consist of components running simultaneously and sharing access to resources provided by the execution platform. For instance, embedded control software in various domains, ranging from household robotics through operation of smart power-grids to on-board satellite software, commonly comprises, in addition to components responsible for taking the control decisions, a set of components driving the operation of sensing and actuation devices. These components interact through buses, shared memories and message buffers, leading to resource contention and potential deadlocks compromising mission-and safety-critical operations. Similar problems are observed in various kinds of software, including system, work-flow management, integration software, web services etc. Essentially, any software entity that goes beyond simply computing a certain function, necessarily has to interact and share resources with other such entities.

The intrinsic concurrent nature of such interactions is the root cause of the sheer complexity of the resulting software. Indeed, in order to analyse the behaviour of such a software system, one has to consider all possible interleavings of the operations executed by its components. Thus, the complexity of software systems is exponential in the number of their components, making a posteriori verification of their correctness practically infeasible. An alternative approach consists in ensuring correctness by construction, through the application of well-defined design principles [BCK12; Gam+94], imposing behavioural contracts on individual components [Ben+12] or by applying automatic transformations to obtain executable code from formally defined high-level models [Sif12].

#### 1.1 The Rigorous System Design approach

The Rigorous System Design (RSD) [Sif12] approach enforces multiple levels of separation of concerns. It relies on a sequence of semantics-preserving transformations to obtain an implementation of the system from a high-level model, while preserving all the properties established along the way.

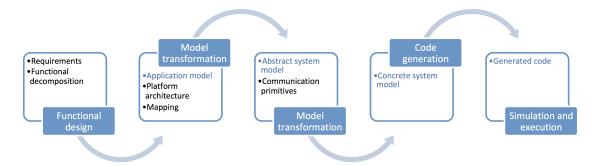

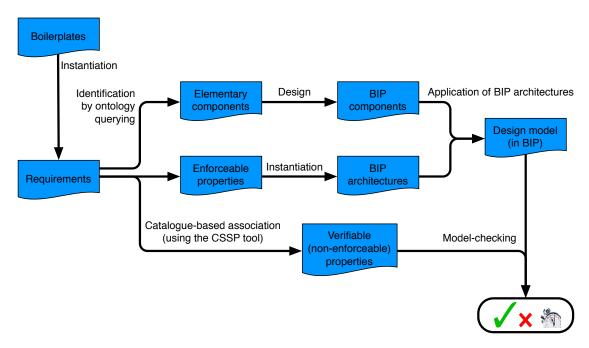

Figure 1.1 illustrates a simplified instantiation of the RSD flow. One starts by designing the *application model*. The application model is verified to prove the elementary properties that are not assured by construction, such as absence of local deadlock, and satisfaction of basic requirements. These elementary properties, serve as a basis for the proof of global properties, obtained by construction.

The application model is then extended with additional components modelling the target platform to obtain the *system model*, which is used to perform platform specific analyses and the optimisation of performance through the exploration of the design space (memories, buses, mapping of software components to hardware elements etc.).

Finally, the model is enriched with platform specific information (e.g. communication primitives) and, after removing components modelling hardware elements, executable code is automatically generated.

Proving that the assumptions made at the modelling level to justify the separation of concerns hold, indeed, at the platform level, guarantees that all the properties established throughout the design process also hold for the generated code.

Figure 1.1: A simplified example of the RSD flow instantiation (the blue items are the result of the previous stage; the black ones are provided as new input at the current stage)

Thus, the RSD approach applies—on the higher abstraction level of the system design process—the same principles as those provided by standard compilers for the generation of machine-executable code from programs written in languages such as Java or C++. It consists in decomposing the argument justifying the correctness of the entire process into several independent arguments justifying the correctness of individual transformations. Furthermore, it provides flexibility w.r.t. the target platforms by postponing design choices as far as possible and allowing for different transformations of the same model to be applied at every design stage. However, in drawing this parallel, it is appropriate to differentiate between commonly used compilers such as gcc, where the public trust originates mainly from the extensive usage experience, and verified compilers such as CompCert [Ler+16], where preservation of semantics at the various stages is formally verified. Although the second scenario is currently preferable for RSD tool-sets due to lack of usage history comparable to that of compilers such as gcc, both can be relevant in practice.

**Applications** Although the RSD approach as formulated by Sifakis [Sif12] originates from the development of the BIP framework for the Embedded Software design (see, for example, [BBS06; Bas+08]), it is applicable in a much broader variety of domains, whereof I will mention below just a few.

In [Bli+19], we have discussed the key issues of applying the RSD approach to the Cyber-Physical Systems (CPSs), which comprise components with both discrete and continuous underlying dynamics. In this context, we have argued that the "objective of cyber-physical system modeling is two-fold. Firstly, simulation of such models provides means for validating the system design. [...] The second objective of cyber-physical systems design is to provide the means for the generation of executable code for the discrete control sub-system." The key point here is that the two design artefacts, i.e. the simulator and the code of the control sub-system, are obtained through two branches of the design flow sharing a substantial prefix. Thus, the generated control sub-system is equivalent to the corresponding components of the simulator by construction.

Expanding on the above idea, it is clear that the RSD approach can be of great benefit for system design and operation involving the so-called Digital Twins where simulation becomes "a core functionality of systems by means of seamless assistance along the entire life cycle" [Ros+15].

Autonomous and (self-)adaptive systems constitute another significant domain for the application of the RSD approach. These include, for example, autonomous vehicles, Cloud and IoT applications. Indeed, such systems must react to changing environmental constraints and user requirements. Therefore they are characterised by high dynamicity both of their behaviour and their structure. In particular, this implies that many of the underlying verification problems are

<sup>&</sup>lt;sup>1</sup>The notion of equivalence, here, implicitly refers to the same semantic equivalence of the underlying modelling framework that is preserved by the constituent model transformations of the RSD flow.

undecidable [EN95; Blo+15] emphasizing the need for by-construction correctness provided by the RSD approach.

The main theme of my current research project aims for adapting the RSD approach to the broad spectrum of general-purpose software development. This target application domain imposes constraints that are fundamentally different from those of the embedded systems design, which had motivated the design choices behind the original BIP framework.

#### 1.2 Structure of the manuscript

This manuscript is structured into three chapters:

- 1. BIP-based Rigorous System Design flow

- 2. A formal study of expressiveness

- 3. The presentation of JavaBIP—a Java flavour of BIP

The first chapter presents and illustrates with the CubETH nanosatellite on-board software case study the RSD approach based on the classical BIP. In the second chapter, I present an algebraic framework for the comparison of expressiveness of component-based systems and its use for a study of the expressiveness of BIP. This informs the choice of the coordination mechanisms for subsequent work. The third chapter presents the design choices and the implementation of JavaBIP.

The three chapters are mostly independent and can be read individually or out of order. The only notable exception is that the fundamental principles of BIP are presented only in Chapter 2 (Section 2.1).

#### BIP-based Rigorous System Design flow

Based on the observation that a posteriori verification is not feasible for most realistic concurrent systems, the RSD approach aims at enforcing desired behavioural properties by construction. This is achieved, essentially, by applying a sequence of semantics-preserving model transformations progressively realising design choices appropriate at each level. This has an additional benefit of postponing design choices as much as possible and, thereby, ensures that optimal solutions are not discarded arbitrarily.

Thus, the RSD approach relies on two fundamental elements:

- a unifying component-based framework with formally defined operation semantics is necessary to define and reason about semantics-preserving model transformations, and

- a method for designing correct high-level models based on informal requirements to initiate the process

In this chapter, I present 1) the classical semantics of BIP—the component framework underlying the approach, 2) the theory of architectures—the key ingredient of the design approach, which allows combining predefined BIP design patterns to enforce desired behavioural properties on the resulting system, and 3) the resulting design process going from a list of system requirements to the C++ implementation.

#### A formal study of expressiveness

In order to understand the applicability limits of the proposed design approach, one has to study the expressive power of the underlying component-based framework. However, for such a study to be possible a proper comparison framework has to be developed. Indeed, most expressiveness studies focus on two questions: 1) what can be computed? and 2) how concise is the program? The first question is typically answered by a comparison to the computing power of Turing machines. The answer to the second question can be summarised—admittedly in a somewhat simplistic manner—by saying that parts of a language represent syntactic sugar w.r.t. another language. None of these two approaches captures the essence of component-based design, where given composition operators are applied to a set of components to build a system without changing the components themselves.

In this chapter, I present 1) a formal algebraic framework that allows the comparison of the expressive power of component-based frameworks, 2) its application to a study of the expressiveness of the BIP framework, and 3) an alternative, "offer" semantics of BIP and its relation with the classical one.

#### **JavaBIP**

This chapter presents JavaBIP—a Java implementation of BIP-inspired coordination mechanisms aimed at general purpose software engineering rather than the design of embedded systems.

The main challenge comes from the fact that, in the context of general purpose software engineering, one cannot expect developers to take a disciplined essentially top-down approach relying exclusively on high-level models and semantics-preserving transformations. The key reasons are

1) the complexity of the software stack and, in particular, the broad use of existing libraries and frameworks, and 2) rapid code evolution due, for example, to the application of agile development methodologies.

We have addressed this challenge by moving away from the code generation paradigm, relying instead on Java annotations and reflection mechanisms to define BIP models associated to Java objects.

In this chapter I present 1) the coordination mechanisms adopted in JavaBIP, 2) the modular architecture used for the JavaBIP implementation, 3) the mechanism allowing to add and remove components from the system dynamically, and 4) two applications—currently under development—in the domains of Cloud Computing and Software Variability, respectively.

#### I or We?

Most of the material presented in this manuscript results from collaborations that I had with many people. I have, therefore decided to use "we" when presenting that material and "I" in the parts specific to this manuscript.

# BIP-based Rigorous System Design flow

The RSD approach relies on two fundamental elements. Firstly, a unifying component-based framework with formally defined operational semantics is necessary to define and reason about semantics-preserving model transformations. On the one hand, such a unifying framework must be expressive enough to allow modelling of a broad spectrum of systems. On the other hand, it must be simple enough to facilitate the formulation and verification of proofs. Secondly, methods and tools for the design of correct-by-construction high-level models are necessary to initiate the process. Although it is difficult to imagine a unique approach that would fit all the various application domains, it seems reasonable to expect that these approaches will share a common core, comprising, at the very least, some form of 1) requirement elicitation and formalisation and 2) (semi-)automatic synthesis of parts of the models in order to discharge these requirements.

In this chapter, I present

- an overview of the Behaviour-Interaction-Priority (BIP) component-based modelling framework that underlies the rest of the work discussed in this manuscript,

- an overview of the theory of architectures—the key ingredient of the design approach, which allows combining predefined BIP design patterns to enforce desired behavioural properties on the resulting system

- an ontology-based design process, developed in the Catalogue of System and Software Properties (CSSP) project, going from a list of system requirements to the C++ implementation.

## 2.1 The BIP component framework

In this section, I will provide brief overviews, first, of the classical operational semantics of BIP as it was initially published in [BS07], then, of connectors that are used to assemble systems from components [BS07; BS08b; BS10].

#### 2.1.1 The basic model

We consider an algebra of components, i.e. an algebraic structure

$$\mathbf{A} ::= C \mid o\langle C_1, \dots, C_n \rangle, \qquad C \in \mathbf{C}, C_1, \dots, C_n \in \mathbf{A} \text{ and } o \in \mathbf{G},$$

generated by a set of composition (glue) operators G from a set of atomic components C. Semantics of components is defined by a partial mapping  $\sigma : A \to B$ , where B is a behaviour type.<sup>2</sup>

<sup>&</sup>lt;sup>1</sup>A more detailed formalisation will be provided in Chapter 3.

<sup>&</sup>lt;sup>2</sup>The mapping is partial to account for the possibility that some syntactically correct terms might not be correct semantically.

#### Component model

The behaviour type of BIP is the set of Labelled Transition Systems (LTS).

**Definition 2.1.1.** A labelled transition system (LTS) is a quadruple  $(Q, P, \rightarrow, q^0)$ , where Q is a set of states, P is a set of ports,  $q^0 \in Q$  is the initial state and  $\rightarrow \subseteq Q \times 2^P \times Q$  is a set of transitions labelled by sets of ports, such that only self-loops can be labelled by the empty set of ports, i.e.  $(q, \emptyset, q') \in \rightarrow$  implies q = q'. For  $q, q' \in Q$  and  $a \in 2^P$ , we write  $q \xrightarrow{a} q'$  for  $(q, a, q') \in \rightarrow$ . A label  $a \in 2^P$  is active in a state  $q \in Q$  (denoted  $q \xrightarrow{a}$ ), if there exists  $q' \in Q$  such that  $q \xrightarrow{a} q'$ . We abbreviate  $q \xrightarrow{a} \xrightarrow{def} \neg (q \xrightarrow{a})$ .

By abuse of notation, we define the binary relation  $\to \subseteq Q \times Q$  as  $q \to q' \stackrel{def}{\Leftrightarrow} \exists a \subseteq P : q \stackrel{a}{\to} q'$  and denote by  $\stackrel{*}{\to}$  its reflexive transitive closure. A state  $q \in Q$  is reachable in the LTS if  $q^0 \stackrel{*}{\to} q$ .

Intuitively, transitions labelled by  $\emptyset$  represent idling: a component that remains idle should not change state, hence the restriction to self-loops. Notice that we distinguish idling from unobservable internal transitions, which we do not model explicitly. To model unobservable transitions, one can use a reserved label, e.g.  $\tau$  or  $\varepsilon$ , and restrict the ways it can be synchronised with other transitions. This is the approach traditionally taken in the literature [Mil89; Hoa85].

Atomic BIP components are those defined directly as LTSs:  $\mathbf{C} \stackrel{\text{def}}{=} \{(P, B) \mid B = (Q, P, \rightarrow, q^0)\}$ . The semantics of atomic components is given by their behaviour:  $\sigma(P, B) \stackrel{\text{def}}{=} B$ . The set of ports P is the *interface* of a component (P, B).

Note 2.1.2. When speaking of a set of LTSs  $B_i = (Q_i, P_i, \rightarrow_i, q_i^0)$ , for  $i \in [1, n]$ , it is common to assume that all  $Q_i$  and  $P_i$  are pairwise disjoint, i.e.  $i \neq j$  implies  $Q_i \cap Q_j = P_i \cap P_j = \emptyset$ . When the indices are clear from the context, we drop them on transition relations and simply write  $\rightarrow$  as, for example in  $q_i \stackrel{a}{\longrightarrow} q_i'$ .

Furthermore, for given pair-wise disjoint sets of ports  $P_i$ , with  $i \in [1, n]$ , we will always denote  $P \stackrel{\text{def}}{=} \bigcup_{i=1}^{n} P_i$ .

#### Glue operators

BIP glues consist of two layers. *Interaction models* define the sets of allowed *interactions*, i.e. synchronisations between the transitions of their operand components. *Priority models* define the conflict resolution policies, reducing non-determinism when several synchronisations allowed by the interaction model are enabled simultaneously.

**Interaction models** For a set of ports P, an interaction model is a set of interactions  $\gamma \subseteq 2^P$ . A compound component  $\gamma(C_1, \ldots, C_n)$  is obtained by applying an interaction model  $\gamma$  to a set of (not necessarily atomic) components  $C_1, \ldots, C_n$ .

Intuitively, an interaction a allowed by the interaction model  $\gamma$  can be fired when all the components involved in a are ready to fire the corresponding transitions. All the components that are not involved in a remain in their current states.

Assuming  $\sigma(C_i) = (Q_i, P_i, \rightarrow_i, q_i^0)$ , for  $i \in [1, n]$ , the semantics of the application of an interaction model  $\gamma$  to components  $C_1, \ldots, C_n$  is defined by putting  $\sigma(\gamma \langle C_1, \ldots, C_n \rangle) \stackrel{\text{def}}{=} (Q, P, \rightarrow_{\gamma}, q^0)$ , with  $Q = \prod_{i=1}^n Q_i$ ,  $q^0 = (q_1^0, \ldots, q_n^0)$  and the smallest transition relation  $\rightarrow_{\gamma}$  satisfying the rule

$$\frac{a \in \gamma \quad \left\{ q_i \xrightarrow{a \cap P_i} q_i' \middle| i \in I \right\} \quad \left\{ q_i = q_i' \middle| i \notin I \right\}}{q_1 \dots q_n \xrightarrow{a}_{\gamma} q_1' \dots q_n'}, \tag{2.1}$$

where  $I = \{i \in [1, n] \mid a \cap P_i \neq \emptyset\}.$

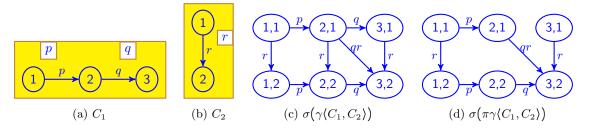

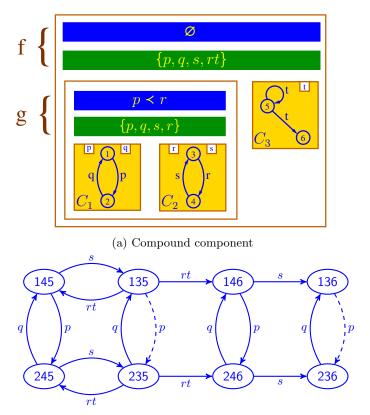

Figure 2.1: Components and behaviour for Examples 2.1.5 and 2.1.6 ( $\gamma = \{p, q, r, qr\}$ ,  $\pi = \{q \prec qr, r \prec qr\}$ )

**Note 2.1.3** (How to read the rule above?). Here and below, we use Structural Operational Semantics (SOS) rules [Plo81] to define the semantics of composition operators.

Each SOS rule consists of a set of whitespace-separated *premises* written above the line and one *conclusion* written below the line. For the sake of clarity, we group some premises in sets. For instance, in the rule (2.1), the second premise is, in fact, itself a set of premises  $q_i \xrightarrow{a \cap P_i} q'_i$ , one for each  $i \in I$ .

In our context, SOS rules should be read as follows. If all premises of the rule are satisfied for a given valuation of the free variables—variables  $a, q_1, \ldots, q_n$  and  $q'_1, \ldots, q'_n$  for (2.1)—then the conclusion must be satisfied as well. Thus, the rule (2.1) can be rewritten as the first order formula

$$\begin{aligned} \forall a \subseteq 2^P, \forall q_1, q_1' \in Q_1, \dots, \forall q_n, q_n' \in Q_n, \\ \left( a \in \gamma \land \exists I = \left\{ i \in [1, n] \,\middle|\, a \cap P_i \neq \varnothing \right\} : \left( \bigwedge_{i \in I} q_i \xrightarrow{a \cap P_i} q_i' \right) \land \left( \bigwedge_{i \notin I} q_i = q_i' \right) \right) \\ \Longrightarrow q_1 \dots q_n \xrightarrow{a}_{\gamma} q_1' \dots q_n'. \end{aligned}$$

Notice that we refer to the *smallest* transition relation that satisfies this rule. This means that the relation  $\rightarrow_{\gamma}$  contains all the transitions that are necessary to satisfy the rule, *and only those transitions*.

**Note 2.1.4.** When the interaction model allows idling, i.e.  $\emptyset \in \gamma$ , the compound component has a self-loop labelled by  $\emptyset$  in every state. The fact that components can have idling self-loops does not introduce any ambiguity in the interpretation of (2.1), since, by Definition 2.1.1,  $q \xrightarrow{\emptyset} q'$  implies q = q'.

**Example 2.1.5.** Consider the two components  $C_1$  and  $C_2$  shown in Figures 2.1a and 2.1b, respectively. We have  $P_1 = \{p, q\}$  and  $P_2 = \{r\}$ . Consider the interaction model  $\gamma = \{p, q, r, qr\}$ . The semantics of the glue operator defined by the interaction model  $\gamma$  is given by the following four rules, obtained by instantiating the rule (2.1), removing premises whereof satisfaction does not depend on the state of the operand behaviours—e.g. when the rule is instantiated with an interaction  $a \in \gamma$ , the corresponding premise is satisfied in all states—and replacing the primed state variables in the conclusions with the unprimed ones whenever the premise of the form  $q_i = q_i'$  should have been used:

$$\frac{q_1 \stackrel{p}{\rightarrow} q_1'}{q_1 q_2 \stackrel{p}{\rightarrow} q_1' q_2}, \quad \frac{q_1 \stackrel{q}{\rightarrow} q_1'}{q_1 q_2 \stackrel{q}{\rightarrow} q_1' q_2}, \quad \frac{q_2 \stackrel{r}{\rightarrow} q_2'}{q_1 q_2 \stackrel{r}{\rightarrow} q_1 q_2'}, \quad \frac{q_1 \stackrel{q}{\rightarrow} q_1' \quad q_2 \stackrel{r}{\rightarrow} q_2'}{q_1 q_2 \stackrel{qr}{\rightarrow} q_1' q_2'}. \tag{2.2}$$

<sup>&</sup>lt;sup>3</sup>We omit the initial states, which are irrelevant for this example.

<sup>&</sup>lt;sup>4</sup>For the sake of clarity, we use the juxtaposition of ports  $\gamma = \{p, q, r, qr\}$  instead of the set notation  $\gamma = \{p\}, \{q\}, \{r\}, \{q, r\}\}$  for interactions.

$\Diamond$

**Priority models** A priority model on an interaction model  $\gamma$  is a strict<sup>5</sup> partial order  $\pi \subseteq \gamma \times \gamma$  (we write  $a \prec b$  as a shorthand for  $(a,b) \in \pi$ ).

Intuitively, an interaction can be fired only if no higher-priority interaction is enabled.

The semantics of the application of a priority model  $\pi$  to a composite component  $C = \gamma \langle C_1, \ldots, C_n \rangle$ , such that  $\sigma(C) = (Q, P, \rightarrow, q^0)$ , is defined by putting  $\sigma(\pi \langle C \rangle) \stackrel{\text{def}}{=} (Q, P, \rightarrow_{\pi}, q^0)$ , with the smallest transition relation  $\rightarrow_{\pi}$  satisfying the rule

$$\frac{q \xrightarrow{a} q' \quad \left\{q \xrightarrow{b} \mid a < b\right\}}{q \xrightarrow{a}_{\pi} q'}.$$

(2.3)

**Example 2.1.6.** Consider again the two components  $C_1$  and  $C_2$  shown in Figures 2.1a and 2.1b, respectively. In addition to the interaction model  $\gamma = \{p, q, r, qr\}$  from Example 2.1.5, consider  $\pi = \{q < qr, r < qr\}$ . The semantics of the glue operator defined by the combination of the interaction model  $\gamma$  and the priority model  $\pi$  is given by the following four rules, obtained by composing the rules (2.2) with rules of the form (2.3), replacing  $q_1q_2 \xrightarrow{qr}$  by  $q_1 \xrightarrow{q}$  or  $q_2 \xrightarrow{r}$  as appropriate:

$$\frac{q_1 \stackrel{p}{\rightarrow} q_1'}{q_1 q_2 \stackrel{p}{\rightarrow} q_1' q_2}, \quad \frac{q_1 \stackrel{q}{\rightarrow} q_1' \quad q_2 \stackrel{r}{\rightarrow}}{q_1 q_2 \stackrel{q}{\rightarrow} q_1' q_2}, \quad \frac{q_1 \stackrel{q}{\rightarrow} \quad q_2 \stackrel{r}{\rightarrow} q_2'}{q_1 q_2 \stackrel{r}{\rightarrow} q_1 q_2}, \quad \frac{q_1 \stackrel{q}{\rightarrow} q_1' \quad q_2 \stackrel{r}{\rightarrow} q_2'}{q_1 q_2 \stackrel{qr}{\rightarrow} q_1' q_2}$$

(2.4)

(the differences with (2.2) are highlighted in red).

The behaviour of the compound component  $\pi\gamma\langle C_1, C_2\rangle$  is shown in Figure 2.1d. Comparing Figures 2.1c and 2.1d it is easy to see that, among the transitions labelled by q, only the transition  $(2,2) \xrightarrow{q} (3,2)$  is enabled and not  $(2,1) \xrightarrow{q} (3,1)$ . Indeed, the negative premise in the second rule of (2.4), generated by the priority q < qr, suppresses the interaction q when the interaction qr is enabled. The same holds for the transition  $(2,1) \xrightarrow{r} (2,2)$  labelled by r.

The priority model in Example 2.1.6 is an instance of the so-called *maximal progress* priority defined by  $\pi \stackrel{\text{def}}{=} \{ a \prec b \mid a, b \in \gamma, \ a \subset b \}$ . Maximal progress priorities are very common in practical examples and, in particular, are used by default in the standard Verimag implementations of BIP.

**Definition 2.1.7.** An *n*-ary *BIP glue operator* is a triple  $((P_i)_{i=1}^n, \gamma, \pi)$ , where  $(P_i)_{i=1}^n$  are pairwise disjoint sets of ports and, denoting  $P \stackrel{\text{def}}{=} \bigcup_{i=1}^n P_i$ , the remaining two elements  $\gamma \subseteq 2^P$  and  $\pi \subseteq \gamma \times \gamma$  are, respectively, interaction and priority models on P.

We omit the sets of ports  $(P_i)_{i=1}^n$  when they are clear from the context.

To simplify the notation, we denote the component obtained by applying the glue operator  $((P_i)_{i=1}^n, \gamma, \pi)$  to sub-components  $C_1, \ldots, C_n$ , by  $\pi \gamma \langle C_1, \ldots, C_n \rangle$  instead of  $((P_i)_{i=1}^n, \gamma, \pi) \langle C_1, \ldots, C_n \rangle$ . Furthermore, when  $\pi = \emptyset$ , we write  $\gamma \langle C_1, \ldots, C_n \rangle$ , omitting  $\pi$ .

#### Priorities do not introduce deadlock

Notice that only interactions belonging to the interaction model of a BIP glue operator can be used in the priority model. This gives the BIP glue operators an important property, which was originally shown in [GS03]: application of a priority model does not introduce deadlocks.

<sup>&</sup>lt;sup>5</sup>As opposed to a (non-strict) partial order, which is a reflexive, antisymmetric and transitive relation, a *strict* partial order is an irreflexive and transitive (hence also antisymmetric) one.

<sup>&</sup>lt;sup>6</sup>Here again, for the sake of clarity, we write  $\pi = \{q < r\}$  instead of  $\pi = \{(q, r)\}$

Figure 2.2: BIP connectors (below each connector, we show the set of interactions it defines)

**Definition 2.1.8.** Let  $B = (Q, P, \rightarrow, q^0)$  be a behaviour. A state  $q \in Q$  is a *deadlock* if holds the statement  $\forall a \subseteq P, q \stackrel{a}{\nrightarrow}$ .

**Lemma 2.1.9** ([GS03]). Let  $C_i$ , such that  $\sigma(C_i) = (Q_i, P_i, \rightarrow, q_i^0)$ , for  $i \in [1, n]$ , be a set of components,  $\gamma$  and  $\pi$  be respectively interaction and priority models on  $P = \bigcup_{i=1}^n P_i$ . A state  $q \in \prod_{i=1}^n Q_i$  is a deadlock in  $\sigma(\pi\gamma\langle C_1, \ldots, C_n \rangle)$  if and only if it is a deadlock in  $\sigma(\gamma\langle C_1, \ldots, C_n \rangle)$ .

*Proof.* The "if" implication is trivial. To prove the "only if" implication, assume that, for some  $a \in \gamma$ , we have  $q \xrightarrow{a}_{\gamma}$ . Let  $b \subseteq P$  be an interaction, maximal w.r.t.  $\pi$ , such that  $b \in \gamma$ , a < b and  $q \xrightarrow{b}_{\gamma}$ . If such b exists, holds  $q \xrightarrow{b}_{\pi}$ . Otherwise holds  $q \xrightarrow{a}_{\pi}$ . In both cases, q is not a deadlock in  $\sigma(\pi\gamma\langle C_1,\ldots,C_n\rangle)$ .

Notice that this proof does not rely on  $\pi$  being a strict partial order. The lemma can be generalised to any *acyclic* relation  $\pi \subseteq \gamma \times \gamma$ .

#### 2.1.2 Connectors and algebras for structuring interaction

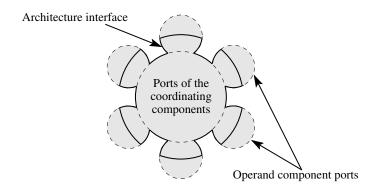

Specifying interaction models as sets of sets of ports is not practical due to their potentially exponential size. An algebra of connectors was introduced in [BS08b] in order to structure interactions in BIP models. *Connectors* are hierarchical, tree-like structures with component ports at the leaves (see Figure 2.2). Connectors define sets of interactions based on the synchronisation attributes of the connected ports, which may be either *synchron* or *trigger* (Figure 2.2a):

- if all connected ports are synchrons, then synchronisation is by *rendezvous*, i.e. the connector defines exactly one interaction, which comprises all its ports (Figure 2.2b);

- if the connector has at least one trigger, the synchronisation is by *broadcast*, i.e. the connector defines the set of interactions comprised by all non-empty subsets of the connected ports containing at least one of the trigger ports (Figure 2.2c).

<sup>&</sup>lt;sup>7</sup>Notice that our use of the terms "broadcast" and "atomic broadcast" (Figure 2.2d) is very different from the meaning commonly used in distributed computing where messages are broadcast to a number of recipients through a network. Here, we use the terms "rendezvous", "broadcast" and "atomic broadcast" for the sake of homogeneity with previous work on BIP (e.g. [BS07]) to denote different kinds of connectors. The use of the term "broadcast" in [BS07] was inspired by previous work on Statecharts [Har87].

Table 2.1: Algebraic representations of the connectors in Figure 2.2: graphical representation (triggers are shown as triangles, synchrons as bullets); interaction models (sets of interactions allowed by each connector); terms of the Algebra of Connectors (triggers are shown by ticks, square brackets indicate sub-connectors); Causal Interaction Trees terms (arrows indicate dependencies,  $\oplus$  indicates independence); Systems of Causal Rules (a valuation of all port variables corresponds to an interaction, variables with value true are exactly those participating in it)

| Connectors                                             | Interaction<br>Models                                    | Algebra of<br>Connectors | Causal<br>Interaction<br>Trees                                                      | Systems of<br>Causal Rules                                         |

|--------------------------------------------------------|----------------------------------------------------------|--------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| p q r                                                  | $\{pqr\}$                                                | pqr                      | pqr                                                                                 | $p \Rightarrow qr$ $q \Rightarrow pr$ $r \Rightarrow pq$           |

| $ \begin{array}{c cccc} \hline p & q & r \end{array} $ | $\{p,pq,pr,pqr\}$                                        | p'qr                     |                                                                                     | $p \Rightarrow true$ $q \Rightarrow p$ $r \Rightarrow p$           |

| p q r                                                  | $ \begin{aligned} \{p,q,pq,pr,qr,\\ pqr\} \end{aligned}$ | p'q'r                    | $ \begin{array}{c} p & q \\ \downarrow & \oplus & \downarrow \\ r & r \end{array} $ | $p \Rightarrow true$ $q \Rightarrow true$ $r \Rightarrow p \lor q$ |

| p $q$ $r$                                              | $\{p,pqr\}$                                              | p'[qr]                   | $\bigvee_{\mathbf{q}r}^{p}$                                                         | $p \Rightarrow true$ $q \Rightarrow pr$ $r \Rightarrow pq$         |

| p q r                                                  | $\{qr,pqr\}$                                             | p[qr]'                   | $qr$ $\downarrow$ $p$                                                               | $p \Rightarrow qr$ $q \Rightarrow r$ $r \Rightarrow q$             |

|                                                        | $\{p,pq,pqr\}$                                           | p'[q'r]                  |                                                                                     | $p \Rightarrow true$ $q \Rightarrow p$ $r \Rightarrow q$           |

The same principle is recursively extended to hierarchical connectors, where one interaction from each subconnector is used to form an allowed interaction according to the synchron/trigger labeling of the connector nodes. For instance the causal chain connector in Figure 2.2d has the port p labeled as a trigger, whereas the binary broadcast subconnector q - r is labeled as a synchron. Thus the causal chain connector allows the singleton interaction p and any interaction that combines p with some interaction of the subconnector q - r. Since the latter allows interactions q and qr, this results in three interactions allowed by the hierarchical connector: p, pq and pqr.

The interaction model is defined as the set of all interactions allowed by at least one of the connectors.

In previous work [BS07; BS10], we have defined and studied several algebraic structures used to represent BIP interaction models, in particular (cf. Table 2.1)

• the Algebra of Connectors—provides a textual notation for connectors equivalent to the graphical notation presented above;

- Causal Interaction Trees—exhibit the causal dependencies among sub-interactions of the interactions allowed by a connector;

- and Systems of Causal Rules—present the causal dependencies as Boolean implications.

Notice that some connectors are equivalent, denoted by the symbol ' $\simeq$ ', meaning that they define the same sets of interactions. For example, the two rendezvous connectors shown in Figure 2.2 —using the Algebra of Connectors notation,  $pqr \simeq p[qr]$ —both allow one same interaction pqr. A slightly more complex example is provided by the two connectors  $p[qr]' \simeq [pq']r$  (the former is the Coordinated broadcast connector from Figure 2.2) both defining the set of two interactions  $\{qr, pqr\}$ . This notion of equivalence is used for studying connector transformations [BS07; BS08b].

Since interaction models are sets of sets of ports, one can consider their characteristic predicates, associating to an interaction model  $\gamma \subseteq 2^P$  the corresponding predicate  $\varphi_{\gamma} \in \mathbb{B}[P]^9$  on the port variables. The predicate  $\varphi_{\gamma}$  is true precisely on such valuations  $v: P \to \mathbb{B}$  of the port variables that  $\{p \in P \mid v(p) = true\} \in \gamma$ . Characteristic predicates of interaction models turn out to be useful for reasoning about architecture composition as presented in Section 2.2 below. Furthermore, the Boolean encoding is also useful for representing interaction models as synchronisation constraints.

Characteristic predicates can be trivially defined in the Disjunctive Normal Form (DNF) as a disjunction of monomials, each representing an interaction. For instance, the characteristic predicate of the interaction model defined by one single connector p'[q'r] (causality chain in Figure 2.2d) is  $\varphi_{\{p'[q'r]\}} = p \overline{q} \overline{r} \vee p q \overline{r} \vee p q r$ . However, it turns out to be more insightful to specify characteristic predicates as conjunctions of causal rules:

$$\varphi_{p'\lceil q'r\rceil} \equiv (p \vee q \vee r) \wedge (q \Rightarrow p) \wedge (r \Rightarrow q).$$

Here, the meaning of the implications  $r \Rightarrow q$  and  $q \Rightarrow p$  is that the participation of the port r in any interaction requires the participation of the port q, which, in turn, requires that of the port p. These two implications expose the causal dependencies visible in the connector structure and, even more so, in the corresponding causal interaction tree (see the last row in Table 2.1). The first conjunct simply states that at least one port must participate in any interaction.

In [BS10], we have shown that the set of interactions defined by any connector can be characterised by a Boolean formula as above, where the implications in each conjunct take the form

$$p \Rightarrow a_1 \vee \cdots \vee a_n$$

with p being a port variable and each  $a_i$  being a conjunction of any number of port variables. We call p the *effect*, whereof  $a_1, \ldots, a_n$  are the *causes*. Indeed, for p to participate in an interaction, all the ports belonging to at least one of  $a_1, \ldots, a_n$  must participate. Thus, we can say that the participation of  $a_i$ , for some  $i \in [1, n]$ , in an interaction is the reason why p can participate.

### 2.2 Architectures: Design patterns for BIP

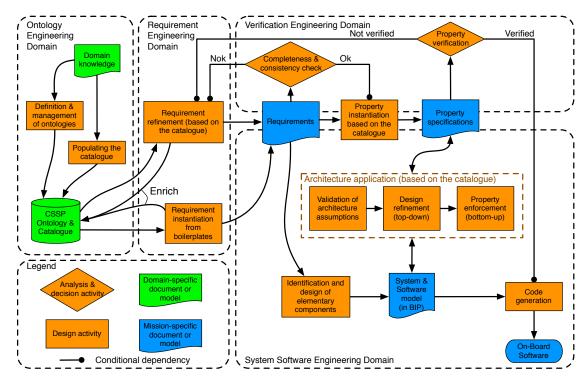

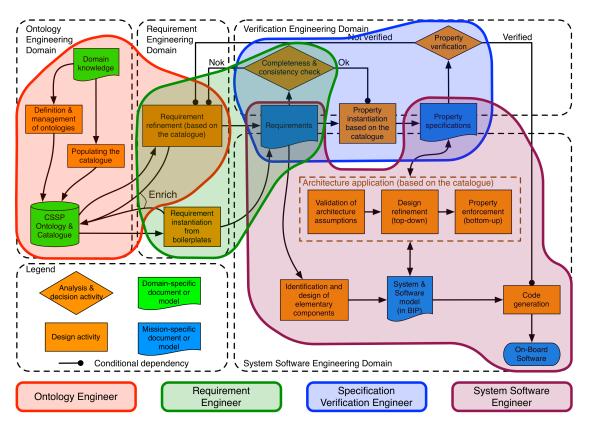

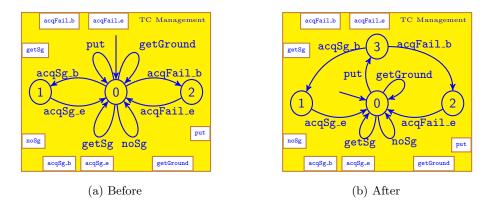

In this section, I will provide an overview of the theory of architectures—formal design patterns that compositionally enforce properties on BIP models—and the RSD flow instantiation based on that theory developed in the *Catalogue of System and Software Properties* (CSSP) project. The objective of the CSSP instantiation of the RSD flow is to provide means for early prototyping of on-board nanosatellite software based on a set of system requirements.

"Architectures depict design principles, paradigms that can be understood by all, allow thinking on a higher plane and avoiding low-level mistakes. They are a means for ensuring global

$<sup>^{8}</sup>$ Omitted in this manuscript for the sake of brevity.

<sup>&</sup>lt;sup>9</sup>I denote  $\mathbb{B} \stackrel{def}{=} \{true, false\}$  and  $\mathbb{B}[P]$  the Boolean algebra generated by the set P.

properties characterising the coordination between components—correctness for free. Using architectures is key to ensuring trustworthiness and optimisation in networks, OS, middleware, HW devices etc." [Att+14; Att+16]

Given an algebra of components  $\mathbf{A}$  (see Section 2.1.1) and some formalism  $L_{\mathbf{A}}$  for the specification of properties (typically, a logic with the corresponding satisfaction relation), property enforcement consists in applying architectures to restrict the behaviour of a set of components so that the resulting behaviour meets a given property. Depending on the expressiveness of the glue operators, it may be necessary to use additional components to achieve a coordination to satisfy the property.

Thus, an architecture is an operator  $A: \mathbf{A}^n \to \mathbf{A}$ , imposing a characteristic property  $\Phi \in L_{\mathbf{A}}$ . It is defined by a glue operator gl and a finite set of coordinating components  $\mathcal{D} \subset \mathbf{A}$ , such that:

- A transforms a set of components  $C_1, \ldots, C_n$  into a composite component  $A(C_1, \ldots, C_n) \stackrel{\text{def}}{=} gl\langle C_1, \ldots, C_n, \mathcal{D} \rangle$ ;

- if  $A(C_1, ..., C_n)$  is semantically valid, it meets the characteristic property  $\Phi$  (recall, Section 2.1.1, that the semantic mapping  $\sigma$  is partial).

Application and platform restrictions entail reduced expressiveness of the glue operator gl that must be compensated by using the additional set of components  $\mathcal{D}$  for coordination. For instance, glue operators defined by BIP connectors (cf. Section 2.1) are memoryless. Hence, they can only be used to impose state properties. Imposing more complex safety properties requires additional coordinating behaviour. Similarly, for distributed architectures, interactions are point-to-point by asynchronous message passing. Synchronisation among the components is achieved by stateful protocols.

An architecture-based design process providing correctness by construction relies on libraries of architectures, each proven to enforce its corresponding characteristic property. Ideally, <sup>11</sup> the design of a system then consists in 1) formalising the system specification as a set of properties; 2) identifying the atomic components that provide the business-specific functionalities; 3) for each property from the system specification, identifying an architecture that enforces that or a stronger property; 4) applying the combination of the identified architectures to the atomic components. Thus, a key fundamental question is how to combine several architectures while preserving all their corresponding characteristic properties? Consider two architectures  $A_1, A_2$ , enforcing respectively properties  $\Phi_1, \Phi_2$  on components  $C_1, \ldots, C_n$ . That is,  $A_1(C_1, \ldots, C_n)$  and  $A_2(C_1, \ldots, C_n)$  satisfy respectively the properties  $\Phi_1, \Phi_2$ . Is it possible to find an architecture  $A(C_1, \ldots, C_n)$  that meets both properties?

In the remainder of this chapter, I will present the instanciation of the notion of architectures for the BIP component framework.

#### 2.2.1 The basic model

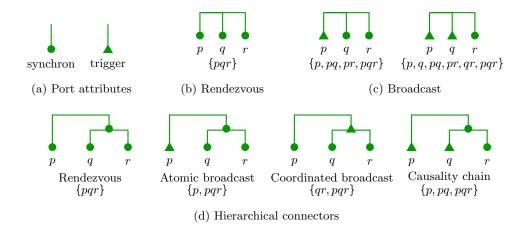

As discussed above, an architecture can be seen as an operator that transforms a set of components into a new composite component. In the context of BIP, it generalises interaction models, by introducing stateful coordinating components. The interface of an architecture is a set of ports that comprises both the ports of the coordinating components and additional dangling ports that must belong to operand components, to which the architecture is applied.

**Definition 2.2.1** (Architecture). An architecture is a tuple  $A = (\mathcal{D}, P_A, \gamma)$ , where  $\mathcal{D}$  is a finite set of coordinating components with pairwise disjoint sets of ports,  $P_A$  is a set of ports, such

$<sup>^{10} \</sup>text{In}$  all examples that we have encountered, coordinating components were atomic, i.e.  $\mathcal{D} \in \mathbf{C}$  (see Section 2.1.1). However, there is no reason to impose this restriction in general.

<sup>&</sup>lt;sup>11</sup>We discuss the deviations from this ideal and their impact on the design process later in the section.

Figure 2.3: A diagram illustrating the relation between ports of an architecture and of its operand components: the inner circle represents the ports of the coordinating components, the "ears" represent the ports of operand components, the representation of the architecture interface is delimited by the solid line

that  $\bigcup_{D\in\mathcal{D}}P_D\subseteq P_A$ , and  $\gamma\subseteq 2^{P_A}$  is an interaction model over  $P_A$ . The ports belonging to  $P_A\setminus\bigcup_{D\in\mathcal{D}}P_D$  are the dangling ports of the architecture.

**Definition 2.2.2** (Application of an architecture). Let  $A = (\mathcal{D}, P_A, \gamma)$  be an architecture and let  $\mathcal{C}$  be a set of components, such that  $\bigcup_{C \in \mathcal{C}} P_C \cap \bigcup_{D \in \mathcal{D}} P_D = \emptyset$  and  $P_A \subseteq P \stackrel{\text{def}}{=} \bigcup_{C \in \mathcal{C} \cup \mathcal{D}} P_C$ .

The application of the architecture A to the set of components  $\mathcal{C}$  is the component  $A(\mathcal{C}) \stackrel{\text{def}}{=} (\gamma \ltimes P)(\mathcal{C} \cup \mathcal{D})$ , where  $\gamma \ltimes P \stackrel{\text{def}}{=} \{a \subseteq P \mid a \cap P_A \in \gamma\}$  is the extension of the interaction model  $\gamma$  to the set of ports P.

Intuitively, an architecture enforces coordination constraints on the components in  $\mathcal{C}$ . The interface  $P_A$  of an architecture A contains all ports of the coordinating components  $\mathcal{D}$  and some additional ports, which must belong to the components in  $\mathcal{C}$  as illustrated in Figure 2.3. In the application  $A(\mathcal{C})$ , the ports belonging to  $P_A$  can only participate in the interactions defined by the interaction model  $\gamma$  of A. Ports that do not belong to  $P_A$  are not restricted and can participate in any interaction. In particular, they can join the interactions in  $\gamma$ .

**Proposition 2.2.3.** For an architecture  $A = (\mathcal{D}, P_A, \gamma)$  and a set of components  $\mathcal{C} \subset \mathbf{A}$  such that  $P_A \subseteq \bigcup_{D \in \mathcal{D}} P_D \cup \bigcup_{C \in \mathcal{C}} P_C$ , the application of A to  $\mathcal{C}$  is valid, i.e.  $\sigma(A(\mathcal{C}))$  is defined.

Clearly, if the interface of the architecture covers all ports of the system, i.e.  $P = P_A$ , the only interactions allowed in  $A(\mathcal{C})$  are those belonging to  $\gamma$ .

Finally, the definition of  $\gamma \ltimes P$  requires that an interaction from  $\gamma$  be involved in every interaction belonging to  $\gamma \ltimes P$ . To allow the ports from  $P \setminus P_A$  to be fired independently in  $A(\mathcal{C})$ , one must have  $\emptyset \in \gamma$ .

Note 2.2.4 (Data). In order to improve their syntactic expressiveness [Fel90], all the formal notions presented so far—namely, BIP components, glue operators and architectures—have been extended to allow the use of local variables in atomic components as well as data transfer among them [Bli+14; BHM19]. However, I will not present these extensions here formally for the sake of conciseness.

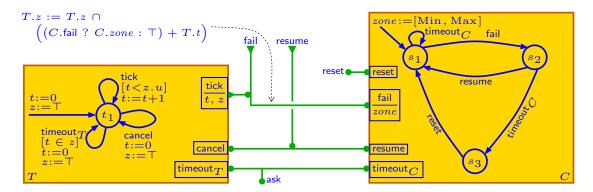

The Failure Monitor architecture example In [BHM19], we have introduced the following refined version of the Failure Monitor architecture from [Mav+16].

We assume given a set of operand components realising a certain business functionality that can *fail* and—following a failure—*resume* operation. When a failure occurs, the Failure Monitor architecture initialises a timer and waits for a duration comprised between Min and Max, which

Figure 2.4: The BIP specification of the Failure Monitor architecture

Table 2.2: Interfaces of the coordinating components of the Failure Monitor architecture

| Component | Local<br>variables | Ports                                | Export function                                                              |

|-----------|--------------------|--------------------------------------|------------------------------------------------------------------------------|

| Timer     | $\{t,z\}$          | $\{tick, cancel, timeout_T\}$        | $\{tick \mapsto \{t,z\}\}$                                                   |

| Control   | $\{zone\}$         | $\{reset, fail, resume, timeout_C\}$ | $   \begin{cases}     \text{fail} \mapsto \\     \{zone\} \}   \end{cases} $ |

are the parameters of the architecture. If by that time the functionality has not been resumed, the architecture issues a request (ask) for the system reset to be triggered externally. <sup>12</sup> These four actions correspond to the four dangling ports of the architecture.

Figure 2.4 shows the coordinating components T (Timer) and C (Control) with the interfaces described in Table 2.2. The export function specifies the local variables that are accessible through each port: variables t and z of the Timer component are accessible only through the port tick. Similarly, variable zone of the Control component is accessible only through the port fail.

Variable t is implicitly assumed to be of type Integer. Variables  $z \stackrel{\text{def}}{=} [z.l, z.u]$  and  $zone \stackrel{\text{def}}{=} [zone.l, zone.u]$  are of type Integer Interval.

The initial states  $t_1$  and  $s_1$ , and valuations  $\sigma_T^0 = \{t \mapsto 0, z \mapsto \top\}$ ,  $\sigma_C^0 = \{zone \mapsto [\text{Min}, \text{Max}]\}$  are shown by the incoming arrows  $\xrightarrow{t:=0,z:=\top} t_1$  and  $\xrightarrow{zone:=[\text{Min},\text{Max}]} s_1$  with  $\top = (-\infty, +\infty)$ .

Transitions are labelled with ports of the corresponding components, Boolean guards and update assignments on local variables. For instance, the loop transition  $t_1 \xrightarrow{\operatorname{tick},[t < z.u],t:=t+1} t_1$  is labelled by the port tick. It is enabled only when the guard [t < z.u] is satisfied by the local variables of the component. Upon firing, this transition increments the value of the local variable t by 1. The guards and update assignments of the transitions of C are omitted. By default, an omitted guard is true and an omitted assignment is empty  $\emptyset$ .

The connector T.tick •• (fail) •• C.fail) of Figure 2.4 defines three interactions (cf. bottom row of Table 2.1), each involving a guard (true) and a transfer of data between the two coordinating components (see the " $T.z := \ldots$ " expression in Figure 2.4). The meaning of the expression C.fail? C.zone : T is the choice between C.zone and T depending on whether the port C.fail participates in the interaction or not. Observe that T + T.t = T and  $T.z \cap T = T.z$ . Thus, the three interactions can be written as follows, simplifying the update assignment of T.z for each

$<sup>^{12}</sup>$ This example originates from the CubETH nanosatellite on-board software case study, where the system reset is performed by the battery sub-system.

interaction separately:

```

(\{T.\mathsf{tick}\}, true, \emptyset),

(\{fail, T.tick\}, true, \emptyset),

(\{C.\text{fail}, \text{fail}, T.\text{tick}\}, true, T.z := T.z \cap (C.zone + T.t)),

```

where  $\varnothing$  denotes the absence of assignment (the relation between variables and assignment expressions is empty).

In this example—as in all practical implementations—we implicitly assume the application of the maximal progress priority  $\mu$ , where  $(a, g, u) \prec_{\mu} (b, h, w)$  if  $a \subset b$  and  $a \neq b$ . For instance, the port T.tick will never fire alone if the port fail is also enabled.

#### 2.2.2Preservation of properties by architecture composition

As discussed in the openning of this section, we need a way of combining several architectures while preserving their respective characteristic properties. Below, we proceed by 1) defining the composition operator, 2) defining the properties, and 3) stating the desired preservation result.

**Definition 2.2.5** (Composition of architectures). Let  $A_i = (\mathcal{D}_i, P_{A_i}, \gamma_i)$ , for i = 1, 2, be two architectures. The composition of  $A_1$  and  $A_2$  is the architecture  $A_1 \oplus A_2 \stackrel{\text{def}}{=} (\mathcal{D}_1 \cup \mathcal{D}_2, P_{A_1} \cup P_{A_2}, P_{A_3})$  $\gamma$ ), where

$$\gamma = \{ a \subseteq P_{A_1} \cup P_{A_2} \mid a \cap P_{A_i} \in \gamma_i, \text{ for } i = 1, 2 \}.$$

(2.5)

Every interaction allowed by  $A_1 \oplus A_2$  must comprise both an interaction allowed by  $A_1$  and an interaction allowed by  $A_2$ . To allow architecture  $A_1$  to progress independently from  $A_2$ , one must have  $\emptyset \in \gamma_2$  and vice-versa.

**Proposition 2.2.6** (Properties of  $\oplus$ ). Architecture composition  $\oplus$  is commutative and associative; it is idempotent if all coordinating components are deterministic;  $A_{id} = (\varnothing, \varnothing, \{\varnothing\})$  is its neutral element, i.e. for any architecture A, we have  $A \oplus A_{id} = A$ . Furthermore, for any component C, we have  $A_{id}(C) = C$ .

Note 2.2.7 (n-ary composition of architectures). Notice that while ⊕ is defined in Definition 2.2.5 as a binary operator, its associativity allows us to speak of the n-ary composition of architectures.

**Definition 2.2.8** (Properties). Let C be a component with  $\sigma(C) = (Q, P, \rightarrow, q^0)$ . A property on C is a state predicate  $\Phi: Q \to \mathbb{B}$ . A state  $q \in Q$  satisfies  $\Phi$ , written  $q \models \Phi$ , if  $\Phi(q) = true$ . A property  $\Phi$  is *initial* if  $q^0 \models \Phi$ . An initial property is an *invariant* if it is satisfied by all reachable states, i.e. holds the formula  $\forall q, (q^0 \xrightarrow{*} q \implies q \models \Phi)$ .

The main idea of our approach is that an architecture enforces its characteristic property on the set of its operand components. From this point of view, the set of coordinating components is not relevant, neither are their states. Thus, to talk about properties enforced by architectures, we consider properties on the unrestricted composition of the operand components as formalized by the following definition.

**Definition 2.2.9** (Enforcing properties). Let  $A = (\mathcal{D}, P_A, \gamma)$  be an architecture, let  $\mathcal{C}$  be a set of components and let  $\Phi$  be a property of their parallel composition  $A_{id}(\mathcal{C})$  (see Proposition 2.2.6). The lifting of  $\Phi$  to  $A(\mathcal{C})$  is defined as  $A(\Phi) \stackrel{\text{def}}{=} \{ (q_c, q_d) \mid q_c \in \Phi, q_d \in \prod_{D \in \mathcal{D}} Q_{\sigma(D)} \}$ . We say that A enforces  $\Phi$  on  $\mathcal{C}$  if,  $A(\Phi)$  is an invariant of  $A(\mathcal{C})$ .

$<sup>^{13}</sup>$ Here—and below in similar contexts—we assume given an equivalence relation on the behaviour type  $\bf B$ , which is then canonically extended to components and architectures. For the sake of simplicity, we write '=' implying equality up to this semantic equivalence. Explicit formalisation will be provided in Chapter 3.

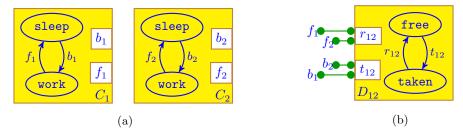

Figure 2.5: Components (a) and architecture (b) for the Mutual Exclusion architecture example

According to the above definition, when we say that an architecture enforces some property  $\Phi$ , it is implicitly required that  $\Phi$  be initial on the coordinated components. Below, we omit mentioning this explicitly.

**Theorem 2.2.10** (Preserving enforced properties). Let C be a set of components; let  $A_i = (\mathcal{D}_i, P_{A_i}, \gamma_i)$ , for i = 1, 2, be two architectures enforcing on C the properties  $\Phi_1$  and  $\Phi_2$  respectively. The composition  $A_1 \oplus A_2$  enforces on C the property  $\Phi_1 \wedge \Phi_2$ .

#### Safety or invariants?

For the sake of clarity I follow here the original papers [Att+14; Att+16], in speaking of invariants rather than of safety properties in full generality. However, the proof of this theorem [Att+16, Theorem 1] is also valid for linear-time safety properties. Furthermore, it can be straightforwardly generalised to branching-time safety.

As a consequence, our definition of properties does not limit the formalisms that can be used for their specification. For instance, in our case studies, we use Computation Tree Logic (CTL).

Consider the special case, where the architecture  $A = (\mathcal{D}, P_A, \gamma)$  is expected to be applied to a set of components implementing certain interfaces. Formally, this means that the set of the dangling ports  $P_A \setminus \bigcup_{D \in \mathcal{D}} P_D$  is partitioned into sets of ports  $P_1, \dots P_n$  belonging to different operand components. It is common for the characteristic property of A to be specified in some logic as an implication of the form  $\bigwedge_{i=1}^n \Phi_n \Rightarrow \Psi$ , where each of  $\Phi_i$  is a formula over  $P_i$ . In such case, the properties  $\Phi_i$  are called the assumptions of the architecture, whereas  $\Psi$  is the guarantee it provides. This separation is useful, since it allows decomposing the design process into two phases: 1) the assumptions  $\Phi_i$  of the architecture are asserted on the operand components—either they are enforced by previous application of architectures or verified by model checking, which, in such case, only concerns a small sub-system of the entire system; 2) the guarantee  $\Psi$  is enforced by the application of the architecture.

The Mutual Exclusion architecture example In order to illustrate property enforcement and architecture composition, we take a simpler example of an architecture enforcing the mutual exclusion of critical sections of two processes.

Consider the components  $C_1$  and  $C_2$  in Figure 2.5a. In order to ensure mutual exclusion of their work states— $\Phi_{12} = (s_1 \neq \text{work} \lor s_2 \neq \text{work})$ , where  $s_1$  and  $s_2$  are, respectively, state variables of  $C_1$  and  $C_2$ —we apply the architecture  $A_{12}$ , shown in Figure 2.5b. This architecture comprises a coordinating component  $D_{12}$ , and the interaction model  $\gamma_{12} = \{b_1t_{12}, b_2t_{12}, f_1r_{12}, f_2r_{12}\}$ .

$<sup>^{14}</sup>$ More precisely, one should speak of the occurrence of events modelled by the ports in  $P_i$  or the fact of their being enabled or not.

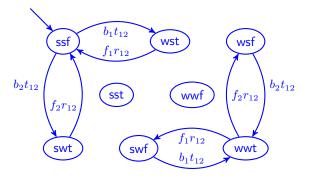

Figure 2.6: Compound behaviour  $\sigma(A_{12}(C_1, C_2))$  (we abbreviate sleep, work, free and taken to s, w, f and t respectively)

The compound behaviour  $\sigma(A_{12}(C_1, C_2))$  is shown in Figure 2.6. Assuming that the initial states of  $C_1$  and  $C_2$  are sleep, and that of  $D_{12}$  is free, neither of the two states (work, work, free) and (work, work, taken) is reachable, i.e. the mutual exclusion property  $\Phi_{12}$  holds in  $A_{12}(C_1, C_2)$ .

Notice that, as discussed above, this claim assumes that, in both operand components, the critical section—modelled by the state work—is "delimited" by the events  $b_i$  and  $f_i$ . Thus, the characteristic property of the architecture  $A_{12}$  can be written in the general case as follows, using CTL:

$$\left( \left( s_1 = \mathtt{sleep} \land s_2 = \mathtt{sleep} \right) \land \bigwedge_{i=1}^2 \mathtt{AG} \; \left( f_i \Rightarrow \mathtt{A} \left[ s_i \neq \mathtt{work} \; \mathtt{W} \; b_i \right] \; \right) \right) \Rightarrow \mathtt{AG} \; \left( s_1 \neq \mathtt{work} \; \lor \; s_2 \neq \mathtt{work} \right).$$

This allows one to abstract from the precise behaviour of the operand components (e.g. as shown in Figure 2.5a). The first conjunct ( $s_1 = sleep \land s_2 = sleep$ ) formalises the global assumption that both components are sleeping in the initial state.

Let  $C_3$  be a third component, similar to  $C_1$  and  $C_2$ , with the set of ports  $\{b_3, f_3\}$ . We define two additional architectures  $A_{13}$  and  $A_{23}$  similar to  $A_{12}$ : they consist, respectively, of coordinating components  $D_{13}$  and  $D_{23}$ , which, up to the renaming of ports, are the same as  $D_{12}$  in Figure 2.5b,  $\gamma_{13} = \{b_1t_{13}, b_3t_{13}, f_1r_{13}, f_3r_{13}\}$  and  $\gamma_{23} = \{b_2t_{23}, b_3t_{23}, f_2r_{23}, f_3r_{23}\}$ . As above,  $A_{13}$  and  $A_{23}$  enforce on  $A_{13}(C_1, C_3)$  and  $A_{23}(C_2, C_3)$ , respectively, the mutual exclusion properties  $\Phi_{13} = (s_1 \neq \text{work} \lor s_3 \neq \text{work})$  and  $\Phi_{23} = (s_2 \neq \text{work} \lor s_3 \neq \text{work})$ .

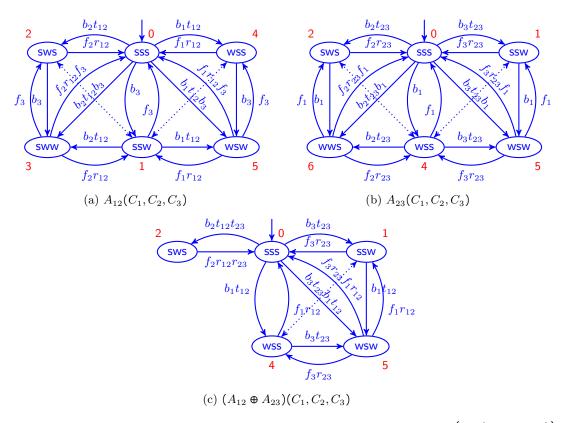

Consider the application of architectures  $A_{12}$  and  $A_{23}$  to the three components  $C_1$ ,  $C_2$  and  $C_3$ . The former enforces the property  $\Phi_{12} = (s_1 \neq \text{work}) \vee (s_2 \neq \text{work})$  (the projection of reachable part of the compound behaviour  $\sigma(A_{12}(C_1, C_2, C_3))$  onto the state-space of the atomic components is shown in Figure 2.7a), whereas the latter enforces  $\Phi_{23} = (s_2 \neq \text{work}) \vee (s_3 \neq \text{work})$  (the projections of reachable states of  $A_{23}(C_1, C_2, C_3)$  onto the state-space of the atomic components are shown in Figure 2.7b). By Theorem 2.2.10, the composition  $A_{12} \oplus A_{23}$  enforces  $\Phi_{12} \wedge \Phi_{23} = (s_2 \neq \text{work}) \vee ((s_1 \neq \text{work}) \wedge (s_3 \neq \text{work}))$ , i.e. mutual exclusion between, on the one hand, the work state of  $C_2$  and, on the other hand, the work states of  $C_1$  and  $C_3$  (see Figure 2.7c). Mutual exclusion between the work states of  $C_1$  and  $C_3$  is not enforced. Furthermore, it is easy to check that  $A_{12} \oplus A_{23} \oplus A_{13}$  enforces mutual exclusion between the work states of  $C_1$ ,  $C_2$  and  $C_3$  as  $\Phi_{12} \wedge \Phi_{13} \wedge \Phi_{23} = ((s_1 \neq \text{work}) \wedge (s_2 \neq \text{work})) \vee ((s_1 \neq \text{work}) \wedge (s_3 \neq \text{work})) \vee ((s_1 \neq \text{work}) \wedge (s_3 \neq \text{work}))$ .

#### 2.2.3 Additional verifications

Contradictory requirements A common problem in practical system design is that of contradictory requirements. For example, the following two properties can be required from an elevator cabin [DG08; PR01]:

Figure 2.7: Projections of reachable states of the compound behaviours onto  $\sigma(A_{id}(C_1, C_2, C_3))$  (for ease of reading, I omit the transitions indicated by dotted blue arrows; furthermore, for ease of comparison between sub-figures, I additionally label each state with a red number, whereof the main label is the binary representation with s = 0 and w = 1)

- If the elevator is full, it must stop only at floors selected from the cabin and ignore outside calls.

- 2. Requests from the second floor have priority over all other requests.

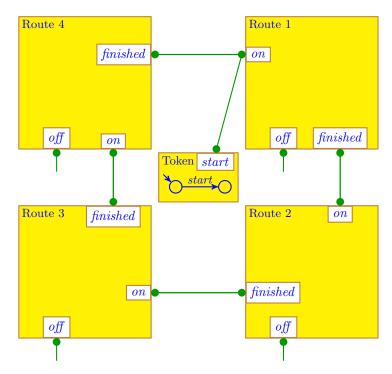

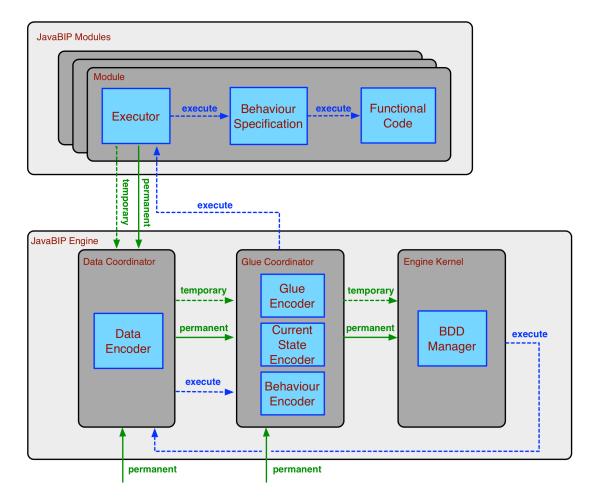

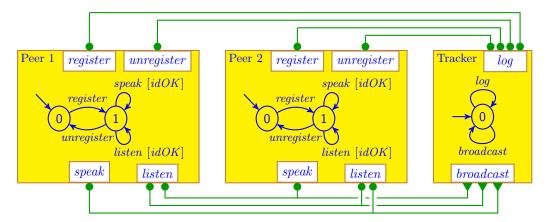

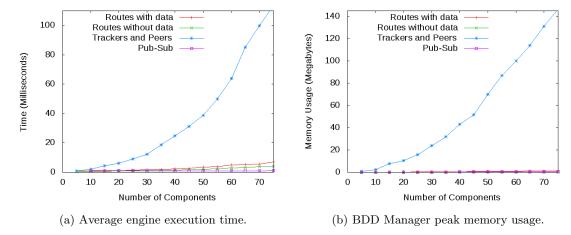

Clearly these two requirements are contradictory, since they cannot be jointly satisfied when the elevator is called from the second floor while it is full. Applying the composition of two architectures enforcing respectively these two properties on the components forming the elevator cabin would generate deadlocks. Thus, although architecture composition  $\oplus$  preserves safety properties, it does not preserve deadlock-freedom. However, deadlock-freedom of BIP models can be verified compositionally [Ben+11].